Sinimulan ng TSMC ang 3nm Production: Isang Mahabang Node sa Power Leading Chips

Ang TSMC noong Huwebes ay nagsagawa ng “Volume Production and Capacity Expansion Ceremony” sa Fab 18 nito sa Southern Taiwan Science Park (STSP). Ang Fab 18 ay kung saan nagaganap ang produksyon ng mga chips gamit ang teknolohiyang proseso ng N3 (3nm-class) nito. Sinasabi ng pandayan na ang mga yield ng 3nm chips na mass produce nito ay maganda at ang pamilya ng mga teknolohiyang N3 nito ay maglilingkod sa mga kliyente nito sa maraming taon na darating.

N3 sa HVM

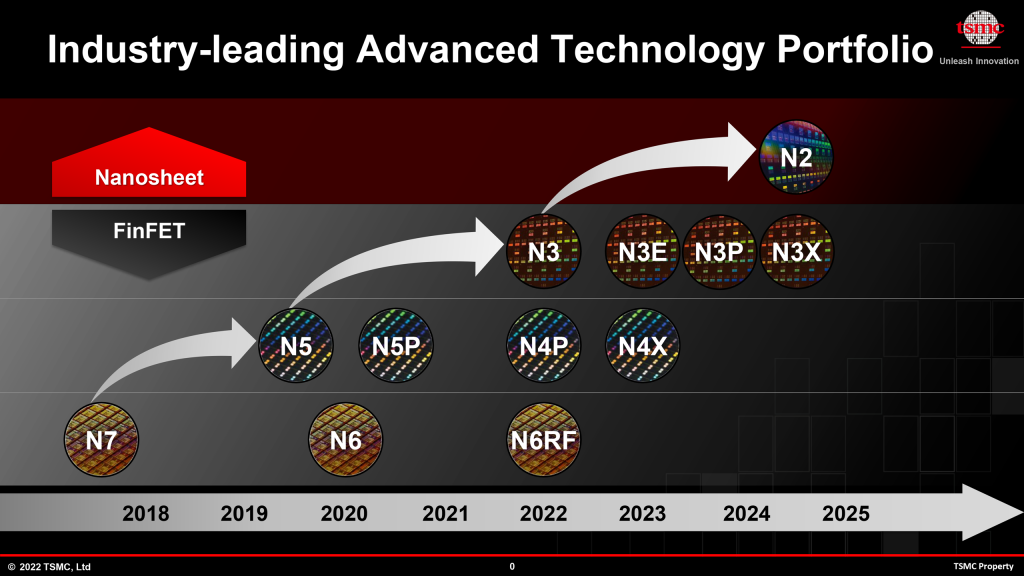

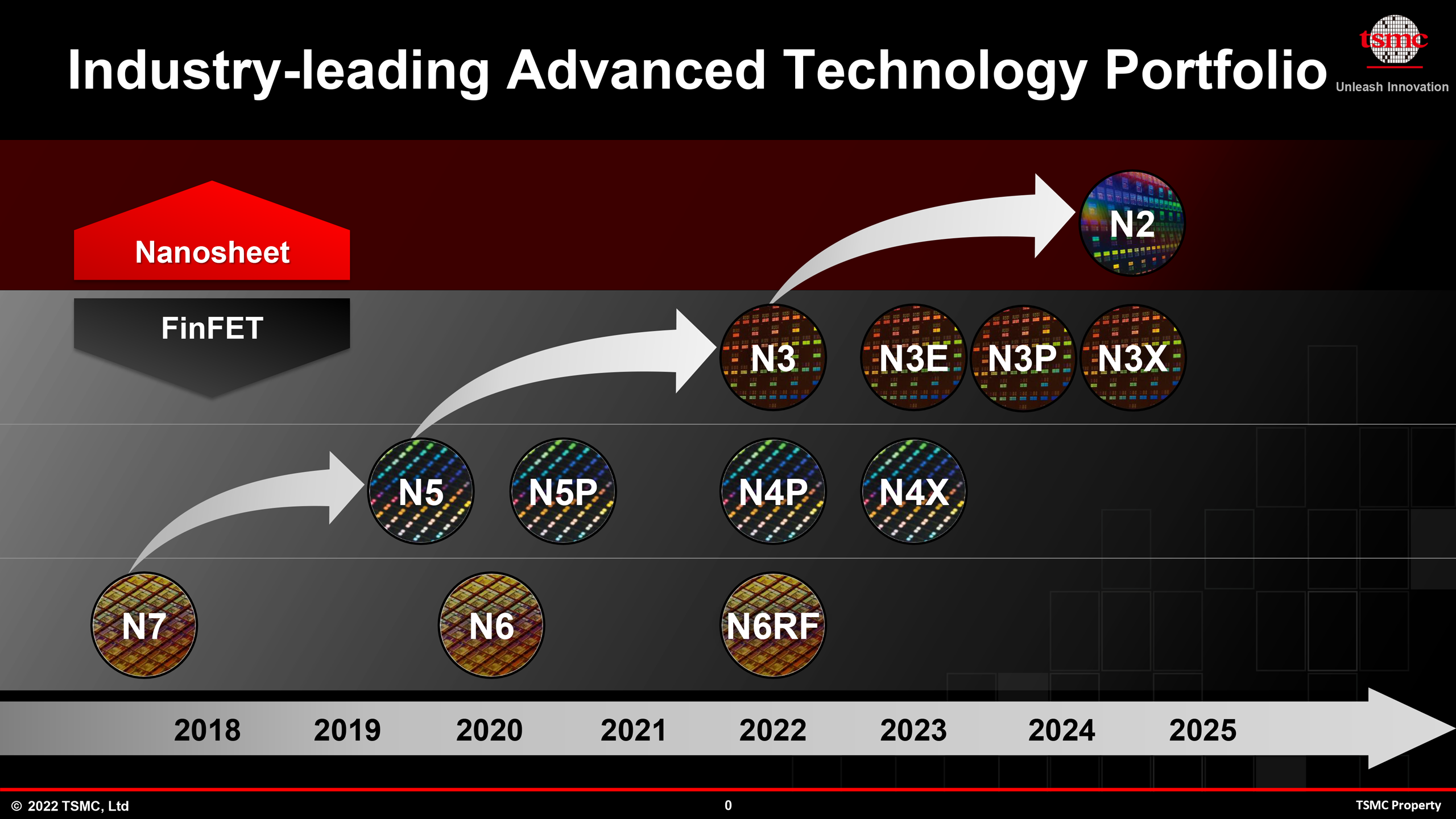

Iniulat na sinimulan ng TSMC ang high volume manufacturing (HVM) sa proseso ng paggawa nito sa N3 noong unang bahagi ng Setyembre. Sa ngayon, ang unang batch ng mga chip ay ginawa at nasubok, kaya ang pormal na anunsyo tungkol sa dami ng produksyon ay karaniwang idinisenyo upang ipakita na ang 3nm-class na proseso ng pandayan ay mabuti para sa mass production at ang mga chips na ginawa dito ay nagbubunga ng ‘maganda.’ Para sa TSMC, ang N3 ay isang napakahalagang pamilya ng mga teknolohiya ng proseso dahil ito ang magiging huling general-purpose node ng foundry batay sa FinFET transistors at isang node na magsisilbi sa mga customer nito nang hindi bababa sa 10 taon. Sa katunayan, sinasabi ng TSMC na ang N3 at ang mga kahalili nito ay gagamitin upang bumuo ng ‘mga produkto na may halaga sa merkado na $1.5 trilyon sa loob ng limang taon’ ng HVM.

Kung ikukumpara sa teknolohiya ng pagmamanupaktura ng N5 ng TSMC, ang N3 production node ng kumpanya ay nangangako na maghahatid ng 10% hanggang 15% na pagpapabuti ng pagganap (sa parehong bilang ng kapangyarihan at transistor), bawasan ang pagkonsumo ng kuryente ng 25% – 30% (sa parehong dalas at pagiging kumplikado) , at pataasin ang logic density ng humigit-kumulang 1.6 beses. Halos hindi nag-aalok ang N3 ng anumang SRAM scaling dahil nagtatampok ito ng laki ng SRAM bitcell na 0.0199 µm^², na ~5% lang na mas maliit kumpara sa 0.021 µm^² SRAM bitcell ng N5.

Mag-swipe para mag-scroll nang pahalangHeader Cell – Column 0 N3E vs N5N3 vs N5Bilis ng Pagpapabuti @ Parehong Kapangyarihan+18%+10% ~ 15%Power Reduction @ Parehong Bilis-34%-25% ~ -30%Logic Density1.7×1.6xSimula ng HVMQ2/Q3 2023 H2 2022

Ang unang pag-ulit ng 3nm-class na mga proseso ng fabrication ng TSMC — N3 na kilala rin bilang N3B — ay inaasahang gagamitin ng mga naunang nag-adopt para sa mga piling aplikasyon lamang dahil iniulat na mayroon itong medyo makitid na window ng proseso. Ito ay maaaring isalin sa mas mababang mga ani para sa ilang mga disenyo. Sa katunayan, ang mga ulat ng media ay nagsasabi na ang karamihan ng mga kliyente ng TSMC ay pumila na ngayon para sa teknolohiya ng pagmamanupaktura ng N3E na nagpapabuti sa window ng proseso, nagpapataas ng pagganap, at higit pang binabawasan ang pagkonsumo ng kuryente, sa halaga ng SRAM scaling (ibig sabihin, mas mababang transistor density). Tila, ang N3E ay nagtatampok ng 0.021 µm^² SRAM bitcell, na may kaunti o walang pagbabago mula sa N5. Mangangahulugan ito ng mas matataas na laki ng die para sa masinsinang disenyo ng SRAM (ang karamihan sa mga CPU, GPU, at SoC).

Nag-aalok ang N3 ng mga chip designer na FinFlex, isang mahusay na paraan para i-optimize ang mga laki ng die at performance/power consumption ng kanilang mga chips. Hinahayaan ng FinFlex ang mga developer na paghaluin at pagtugmain ang iba’t ibang uri ng karaniwang mga cell sa loob ng isang bloke upang tumpak na ma-optimize ang pagganap, paggamit ng kuryente, at lugar, na partikular na pahahalagahan ng mga taga-disenyo ng mga kumplikadong system-on-chips na may posibilidad na samantalahin ang parehong pagganap ng transistor at density ng transistor.

(Kredito ng larawan: TSMC)

Sa kalaunan, plano ng TSMC na magdagdag ng higit pang mga node sa pamilyang N3. Kasama sa mga pinakabagong bersyon ng proseso ang N3P, na nangangako ng pinahusay na pagganap, ang N3S na idinisenyo upang pataasin ang densidad ng transistor, at N3X na may mga pinahusay na boltahe pati na rin ang mga karagdagang pag-optimize ng pagganap para sa mga application tulad ng mga CPU.

Ang mga Customer ay Pumila para sa N3 Sa kabila ng Mataas na Gastos

Ang isang bulung-bulungan ay nagsasabi na halos lahat ng pinakamahalagang customer ng TSMC, kabilang ang AMD, Apple, Broadcom, Intel, MediaTek, Nvidia at Qualcomm ay lahat ay interesado sa paggamit ng mga N3 node ng TSMC, kahit na mahirap sabihin kung kailan ang bawat isa sa mga taga-disenyo ng chip na ito ay tumalon. 3nm bandwagon ng pandayan at kung aling mga produkto. Inaasahan na ang Apple ay isa sa mga unang kliyente na gumamit ng N3 ng TSMC para sa isa sa mga premium na SoC nito, kahit na wala kaming ideya kung aling SoC ito. Samantala, nilalayon ng AMD na gamitin ang N3 para sa ilan sa mga produktong nakabatay sa Zen 5 nito dahil sa 2024, samantalang malamang na gagamitin ng Nvidia ang N3 para sa mga susunod na henerasyong GPU na nakabatay sa arkitektura ng Blackwell dahil sa parehong timeframe.

Ngunit ang paggamit ng N3 ng TSMC ay hindi magiging mura. Ang ilang mga ulat ay nagsasabi na ang contract maker ng mga chips ay maaaring singilin ng hanggang $20,000 bawat wafer na naproseso gamit ang 3nm-class na teknolohiya nito. Siyempre, ang pagpepresyo ng TSMC ay nakasalalay sa maraming mga kadahilanan, tulad ng mga volume, disenyo, at mga detalye, kaya kunin ang numero na may isang butil ng asin.

Samantala, ang mataas na quote ay nangangahulugan na ang mga fabless chip designer ay maaaring mas gusto na magreserba ng TSMC’s leading-edge nodes para sa mga premium na produkto habang gumagawa ng higit pang mga mainstream na device gamit ang isang napatunayang fabrication technology. Halimbawa, ginagamit ng Apple ang proseso ng pagmamanupaktura ng TSMC’s N4 (4nm-class) para lang sa A16 Bionic nito na nagpapagana sa flagship nitong iPhone 16 Pro. Sa kabaligtaran, ang iPhone 14 non-Pro ng kumpanya ay patuloy na umaasa sa A15 SoC mula 2021 na ginawa sa teknolohiyang N5P ng TSMC.

Fab 18 Phase 8

Bilang karagdagan sa pag-anunsyo na ang teknolohiya ng proseso ng N3 nito ay pumasok sa HVM, nagsagawa rin ang TSMC ng seremonya ng topping ng Fab 18 phase 8 na gusali nito. Ginagamit ng kumpanya ang Fab 18 nito para gawin ang pinaka-advanced na chips nito sa N5 at N3 production node nito. Kapag ang Fab 18 phase 8 ay nilagyan ng mga tool sa produksyon, ito ay makabuluhang magpapalawak ng kapasidad ng TSMC para sa. Ang mga nangungunang proseso ng paggawa nito.