Pinag-uusapan ng AMD ang Hybrid Ryzen CPU Concepts, Iniiwasan ang AVX-512 Problem ng Intel

Noong Computex 2023, nagkaroon ako ng pagkakataong bumisita sa matatayog na opisina ng AMD sa Taipei, Taiwan, para makita ang Ryzen AI demo ng kumpanya at makausap si David McAfee, ang Corporate VP at GM ng Client Channel Business. Karamihan sa aming pag-uusap ay nakasentro sa mga pagsusumikap ng AMD sa espasyo ng consumer AI, ngunit nag-ipit din ako sa ilang mga katanungan tungkol sa pagkuha ng AMD sa mga hybrid na CPU. Sinabi sa akin ni McAfee na ang AMD ay may ibang pananaw sa mga hybrid na processor kaysa sa Intel na maiiwasan ang pagiging kumplikado na nagpilit sa Intel na tanggalin ang suporta ng AVX-512 mula sa mga chip nito.

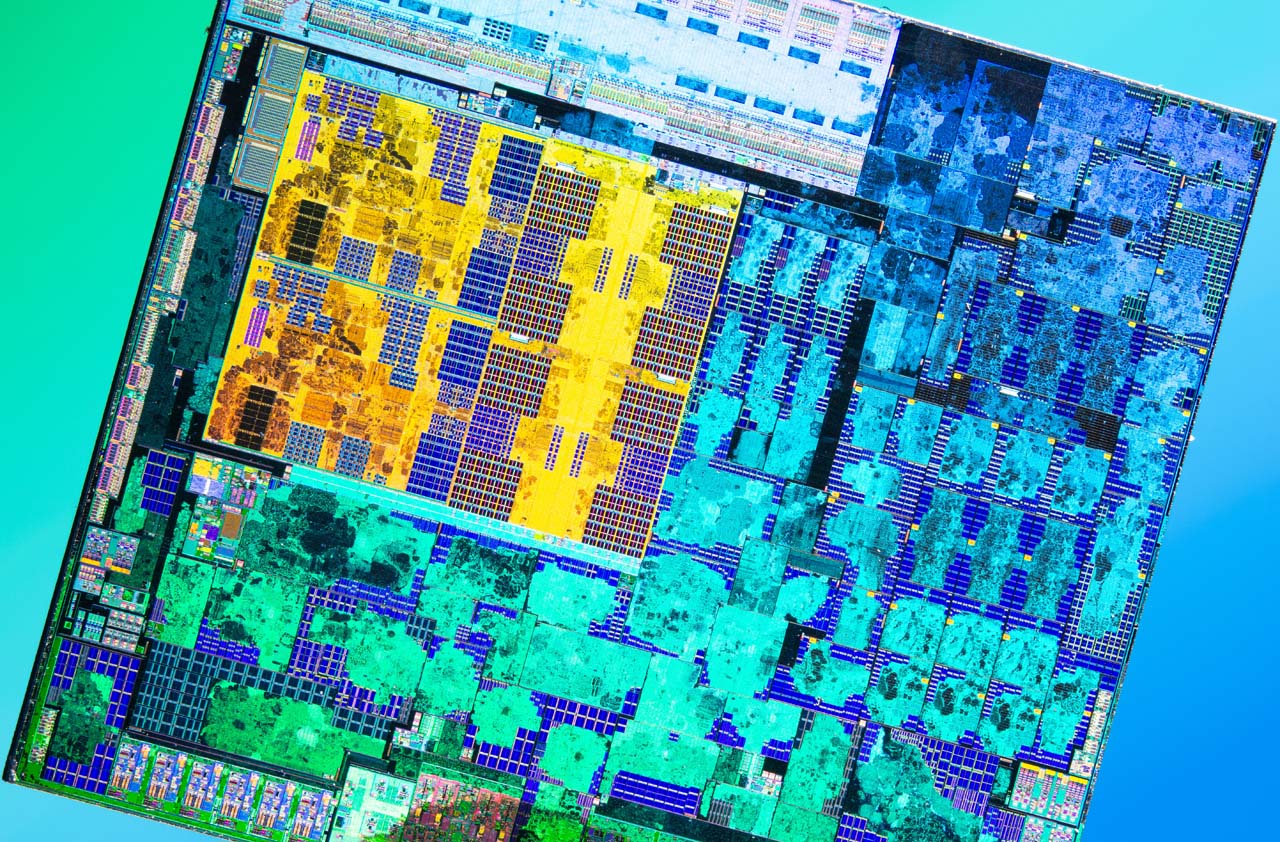

Nakapanayam ko ang AMD CTO Mark Papermaster dalawang linggo na ang nakakaraan sa Antwerp, Belgium. Sinabi niya sa akin na “makikita namin ang mga high-performance core na may halong power-efficient na mga core na may halong acceleration” sa hinaharap na AMD client [consumer] mga processor, na nagpapahiwatig na, tulad ng Intel bago nito, ang AMD ay magpapatibay ng isang hybrid na disenyo ng core ng pagpapatupad ng CPU sa hinaharap. Iyon ay hindi masyadong nakakagulat — nakita namin ang mga unang palatandaan ng dalawang magkaibang uri ng CPU core sa mga manwal ng software ng AMD ilang buwan na ang nakakaraan. Bukod pa rito, inilalagay na ng AMD ang pundasyon kasama ang paparating na EPYC Bergamo chips na may mga siksik na Zen 4c core na katulad ng mga efficiency core.

Ang kasalukuyang Ryzen 7040 na laptop chip ng AMD ay nagtatampok na ng hybrid na disenyo, ngunit hindi sa dalawang magkaibang uri ng mga core ng CPU. Sa halip, ang Ryzen 7040 ay mayroon lamang isang uri ng CPU core na ipinares sa isang in-built na AI accelerator engine na gumagana nang hiwalay sa mga CPU at GPU core. Nagbibigay ang engine na ito ng mga pakinabang para sa ilang partikular na uri ng mga workload ng AI inference, ngunit mas maganda ang CPU at GPU core para sa iba pang uri ng inference. Kaya, ang trick ay idirekta ang iba’t ibang mga workload ng AI sa tamang uri ng mga core upang makuha ang pinakamahusay na performance at power efficiency.

Ang paghahagis ng magkahiwalay na performance at kahusayan na mga core ng CPU sa halo na iyon ay magpapakilala ng isa pang opsyon sa pag-compute para sa AI inference workloads, at tinanong ko si McAfee kung, sa konsepto, magiging posible na ang mga core ng kahusayan ay magiging mas mahusay para sa AI kaysa sa isang dedikadong piraso ng silicon (ang AI makina). Ipinaliwanag ni McAfee na ang mahigpit na pagtutok ng mga AI engine sa mga operasyong partikular sa AI ay magbibigay dito ng kahusayan na kalamangan sa anumang pangkalahatang layunin na pag-compute ng CPU — kahit na isang core ng kahusayan.

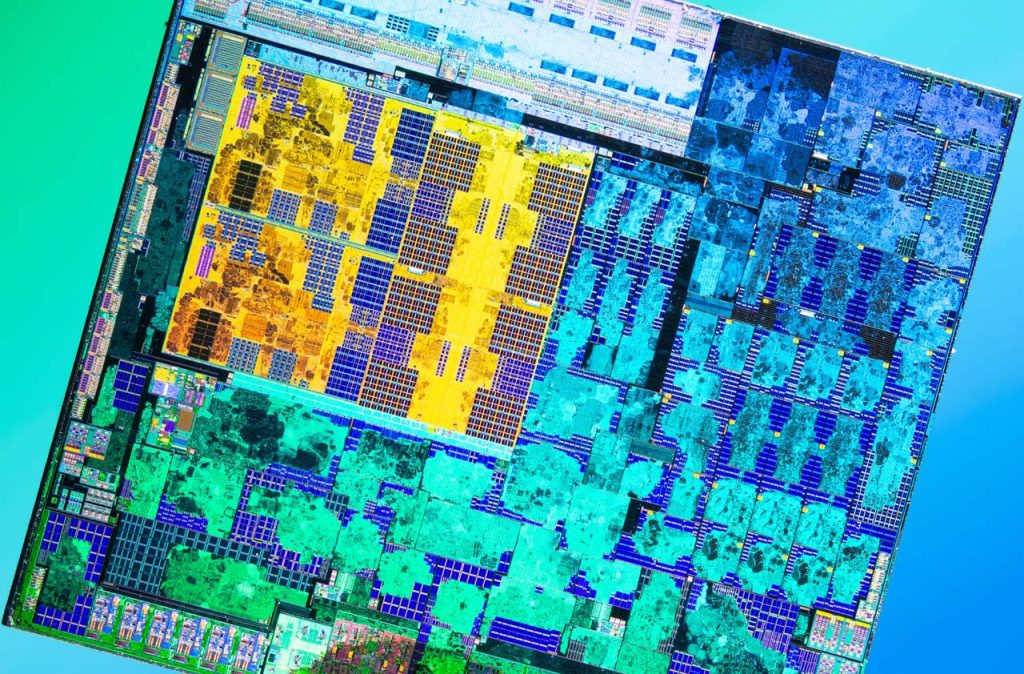

Pagkatapos ay lumipat kami sa pagtalakay sa mga hybrid chip ng Intel, na mayroong dalawang uri ng mga core, bawat isa ay may sariling natatanging microarchitecture. Lumilikha iyon ng mga kagiliw-giliw na problema: Ang mga core ng pagganap ng Intel ay sumusuporta sa AVX-512, ngunit ang mga mas maliit na mga core ng kahusayan ay hindi. Na humantong sa Intel na ganap na hindi paganahin ang suporta ng AVX-512 (sapilitan sa dulo), kaya na-de-featuring ang sarili nitong chip at nag-aaksaya ng mahalagang lugar ng kamatayan.

Tinanong ko si McAfee kung ano ang naramdaman ng AMD tungkol sa diskarteng iyon sa mga hybrid na disenyo.

“Ang sasabihin ko ay ito, sa palagay ko ang paraan ng pag-iisip natin tungkol dito, ang diskarte ng dalawang magkaibang pagganap at mga core ng kahusayan na may ibang magkaibang suporta sa ISA at IPC at kakayahan ay hindi kinakailangang tamang diskarte,” tugon ni McAfee. “Sa tingin ko ito ay nag-iimbita ng higit na kumplikado sa kung ano ang maaaring isagawa kung saan, at habang tinitingnan namin ang iba’t ibang mga opsyon para sa pangunahing disenyo, hindi iyon ang diskarte na aming ginagawa.

“Sa tingin ko habang inilalabas namin ang higit pa nito sa paglipas ng panahon, ang makikita mo mula sa amin ay isang diskarte na isinasaalang-alang ang mga pakinabang na maibibigay ng iba’t ibang pangunahing pag-target, ngunit ginagawa ito sa paraang higit pa, mula sa pananaw ng aplikasyon. , mas homogenous.”

Alam na namin na ang mga core ng kahusayan ng Zen 4C ng AMD, na gagamitin nito sa paparating na mga chip ng server ng Bergamo, ay susuportahan ang parehong mga tagubilin, tulad ng AVX-512, bilang mga ganap na tampok na mga core ng pagganap. Gayunpaman, magkakaroon sila ng cut-down na hierarchy ng cache upang bawasan ang pagkonsumo ng die area. Ang layunin ng parehong mga uri ng pangunahing pagkakaroon ng parehong IPC sa mga core ng pagganap at kahusayan ay mahalaga. Sa kabaligtaran, ang mga core ng kahusayan ng Intel ay may mas mababang IPC kaysa sa mga core ng pagganap nito (na maaaring magresulta sa mga tradeoff sa iba pang mga adhikain nitong e-core, tulad ng Sierra Forest).

“ISA, una sa lahat, ang pagpapanatiling pare-pareho sa kung saan ang isang workload ay maaaring gumana sa anumang core, ay may mga dramatikong pakinabang,” sabi ni McAfee. “At kahit na tumingin ka sa isang Ryzen desktop CPU ngayon, ang paraan kung saan ang Windows scheduler ay plumbed, ang kakayahang tukuyin ang mga core na mas mabilis, mas mabagal, atbp., at idirekta ang mga thread sa iba’t ibang mga core depende sa ranggo o kakayahan sa loob ng isang CPU; Iyan ay isang mahusay na itinatag na pamamaraan na medyo matagal na naming ginagamit. Ito ay humahantong sa, sa aming opinyon, gamit ang isang mekanismo kung saan ang kakayahan ng mga core ay mas pare-pareho.

“Ito ay isang mas sinubukan at totoong paraan upang tingnan ang pagdadala ng maraming iba’t ibang uri ng pangunahing pag-target sa isang disenyo. Sa palagay ko ang diskarte ng Intel ay nag-iimbita ng maraming kumplikado sa paraan ng pagpapatakbo nito. At sa palagay ko ang aming pagsusuri ay iyon. Ako Huwag isipin na makikita mo kaming pumunta sa landas na iyon sa parehong paraan na mayroon sila, kung at pagdating sa isang Ryzen processor.” Pagtatapos ni McAfee.

Hindi tulad ng Papermaster, ang McAfee ay hindi nakikipag-ugnayan sa kung o kailan darating ang hybrid sa Ryzen, at hindi namin alam kung saan unang ipakikilala ng AMD ang isang hybrid na arkitektura kasama si Ryzen, ito man ay may monolithic APU o isa sa mga modelong nakabatay sa chiplet. Gayunpaman, malinaw na ang AMD ay nagnanais ng isang hybrid na hinaharap na maiiwasan ang mga tradeoff na nakita natin sa mga desisyon sa disenyo ng Intel sa likod ng mga processor ng Alder at Raptor Lake.

Ang ilan sa mga sariling desisyon ng AMD ay maaaring malaman sa pamamagitan ng pagsusuri sa mga maling hakbang ng Intel, o maaaring ito ay ang karaniwang kahulugan ng muling paggamit ng IP sa kasalukuyang pangunahing arkitektura — ito ay isang mas magaan na pagtaas upang mag-tweak ng isang microarchitecture kaysa sa pagsisimula sa isang malinis na disenyo. Sa alinmang kaso, ang kakayahang mapanatili ang suporta para sa AVX-512 ay malamang na magbibigay sa AMD ng kalamangan sa pagganap sa mga vectorized na workload, sa kondisyon na hindi sumusunod ang Intel.

Sa kabaligtaran, ang isa ay maaaring magtaltalan na ang diskarte ng Intel sa pagkakaroon ng isang hiwalay na microarchitecture na nakatutok para sa mas mababang kapangyarihan na operasyon ay isang mas mahusay na diskarte, kahit na kung ito ay ipinares sa pare-parehong suporta ng ISA sa parehong mga uri ng mga core. Kung naitama ng Intel ang hindi pagkakatugma ng ISA nito sa Meteor Lake at nagpapanatili ng suporta para sa AVX-512 sa parehong mga pangunahing uri, maaari din itong patunayan na isang makapangyarihang combo.

Sa alinmang kaso, malinaw na habang ang AMD ay magiging pangalawa sa merkado na may hybrid na disenyo, magkakaroon ito ng ibang paraan. Oras lang ang magsasabi kung paano nakasalansan ang dalawang diskarte sa mga benchmark.