Mga Detalye ng Intel PowerVia Backside Power Delivery Technology

Idinetalye ng Intel noong Lunes ang pagpapatupad nito ng backside power delivery network (BS PDN) na magiging bahagi ng mga proseso ng fabrication nitong Intel 18A at 20A (18/20 angstroms, 1.8/2.0nm-class). Bilang karagdagan, nagpahayag din ang kumpanya ng higit pang impormasyon tungkol sa mga benepisyong ibinigay ng teknolohiyang ito para sa panloob nitong Intel 4 + PowerVia node na partikular na idinisenyo sa pinakamahusay na BS PDN.

Paghahatid ng Likod na Power

Ang 18A at 20A na teknolohiya sa pagmamanupaktura ng Intel ay magpapakilala ng dalawang pangunahing inobasyon: RibbonFET gate-all-around field-effect transistors (GAAFETs) at PowerVia backside power delivery network. Ang mga pakinabang ng mga transistor ng GAA ay tinalakay na dati at lampas sa saklaw ng anunsyo ngayon. Sa halip ay magtutuon kami sa backside power delivery.

(Kredito ng larawan: Intel)

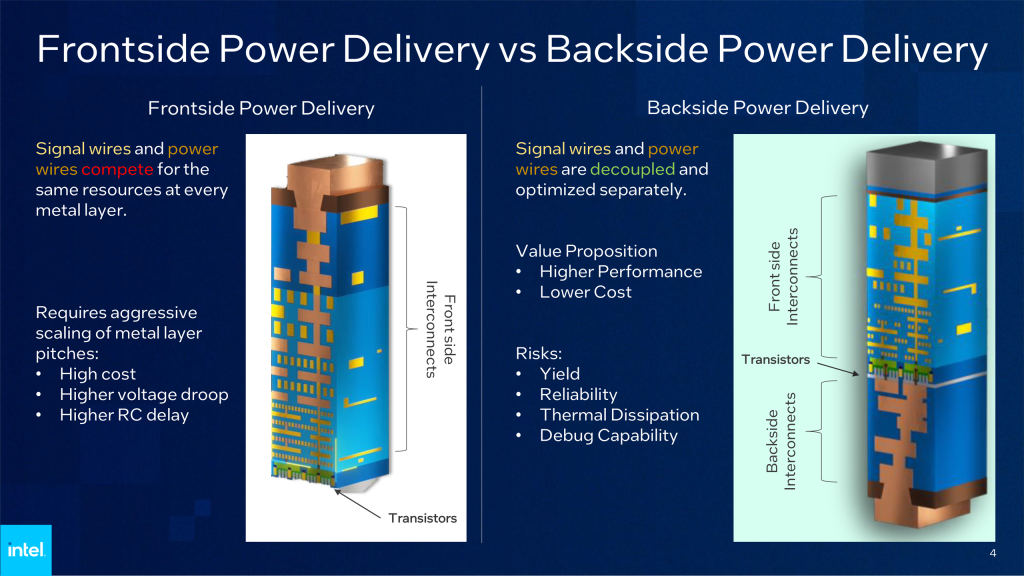

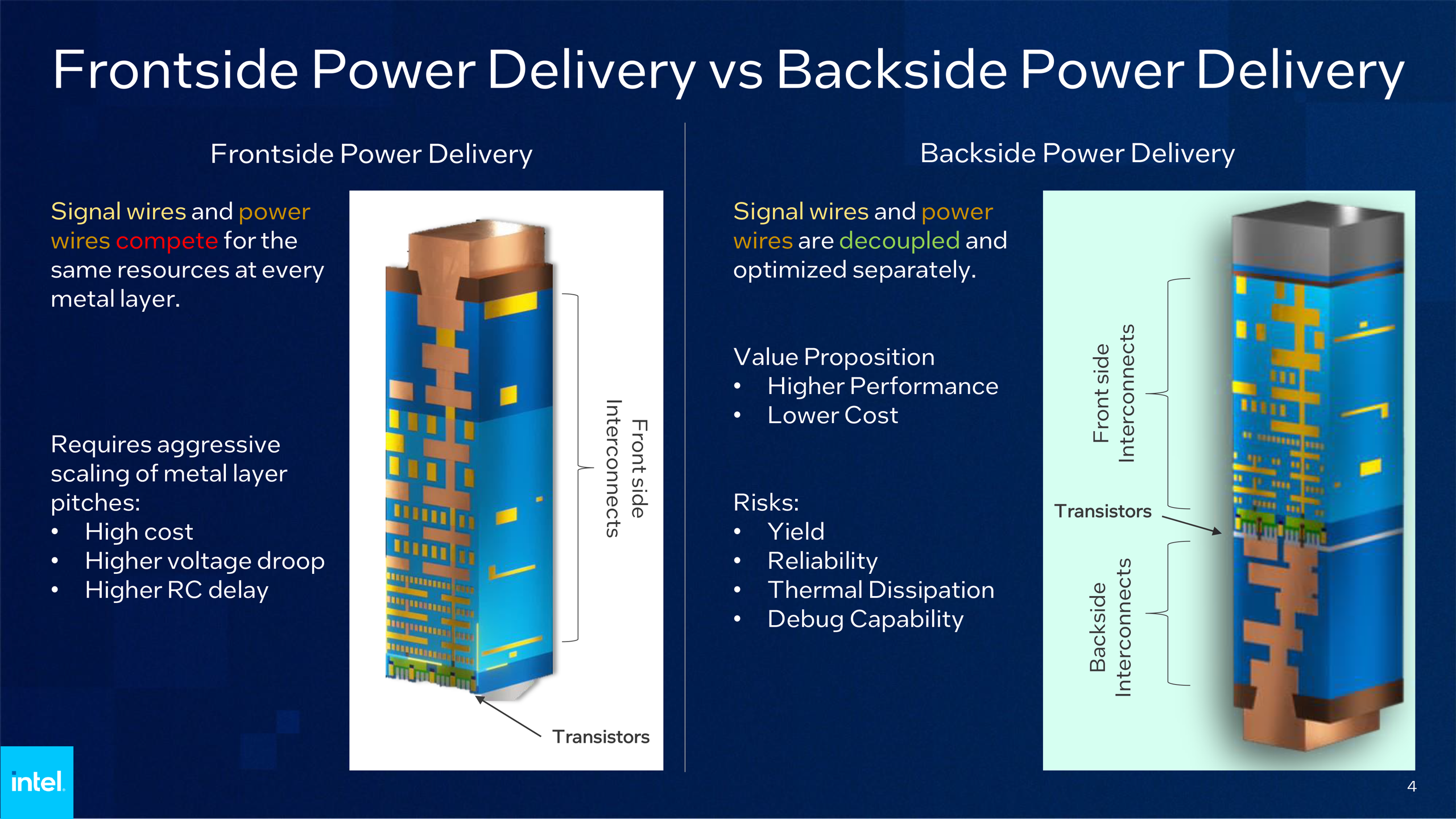

Nilalayon ng backside power rail na paghiwalayin ang power at I/O wiring, na inililipat ang mga linya ng kuryente sa likod ng wafer. Ang pamamaraang ito ay humaharap sa mga problema tulad ng pagtaas sa pamamagitan ng mga resistensya sa back-end-of-line (BEOL), sa huli ay nagpapahusay sa pagganap ng mga transistor at nagpapababa ng kanilang paggamit ng kuryente. Tinatanggal din nito ang anumang posibleng interference sa pagitan ng data at mga power wire at pinatataas ang density ng logic transistor.

Sa paglipas ng panahon, ang BD PDN ay magiging isang karaniwang tampok na chip, ngunit sa ngayon ay itinuturing ito ng Intel na isang pangunahing tagumpay sa pagbabago na katulad ng strained silicon sa 90nm noong 2003, Hafnium-based high-K metal gate sa 45nm noong 2007, at FinFET sa 22nm noong 2012 .

(Kredito ng larawan: Intel)

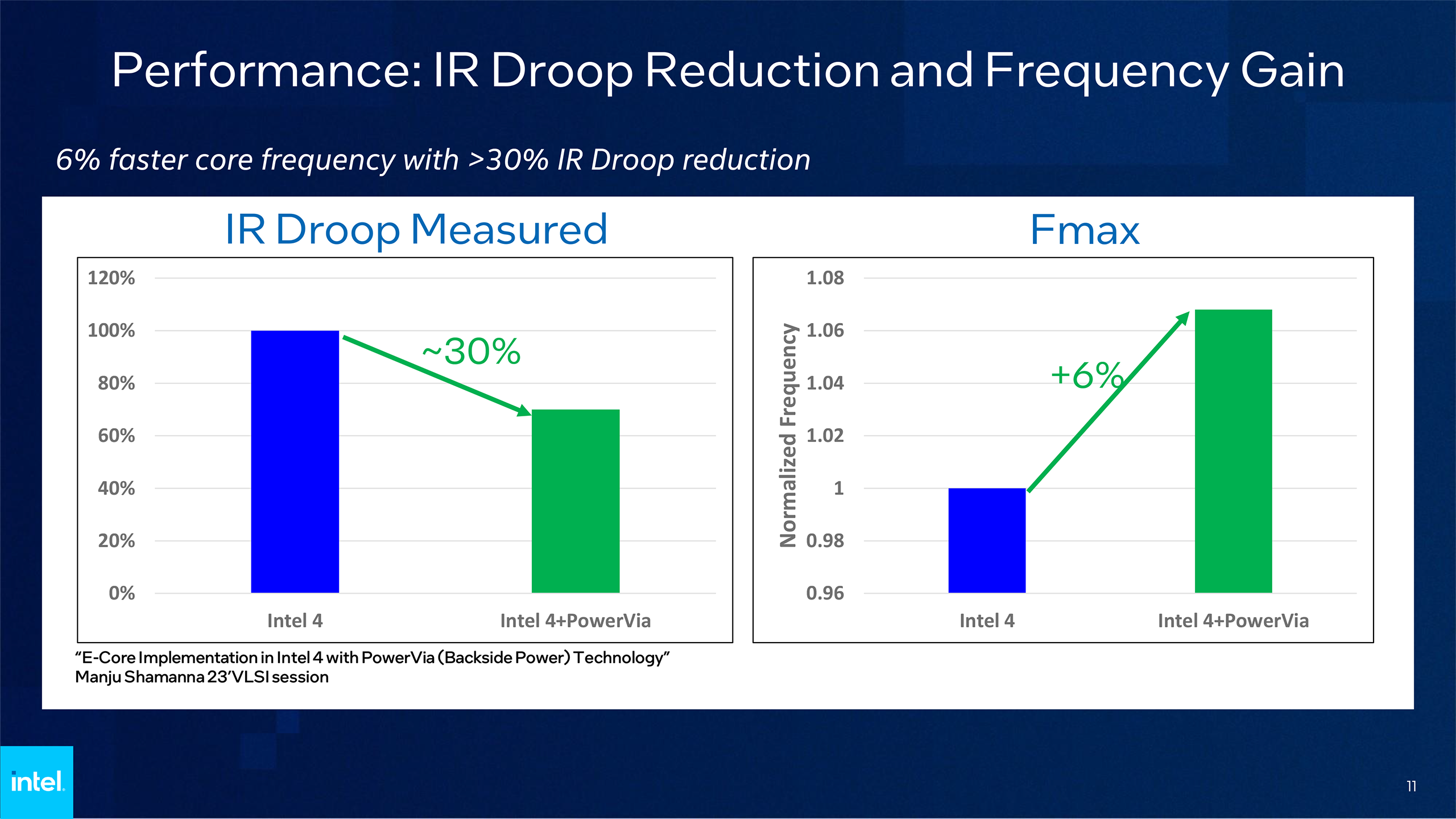

Sinasabi ng Intel na kapag ipinatupad sa isang pagsubok na chip sa isang panloob na node ng proseso, ang likurang bahagi ng PDN nito ay nagpagana nito na pataasin ang bilis ng orasan ng higit sa 6%, nabawasan ang IR boltahe na bumaba ng 30%, at nadagdagan ang paggamit ng cell sa malalaking bahagi ng E-core die nito. sa higit sa 90%. Sa kabila ng mga benepisyo, ang pagpapatupad at pagbuo ng backside power delivery ay isang hamon sa ilang kadahilanan.

Building PowerVia Backside PDN

Ang pagbuo ng backside PDN ay ibang-iba sa tradisyonal na frontside power delivery. Ang paggawa ng kahit na ang pinaka-advanced na chips ay medyo tapat sa mga araw na ito. Ang paggawa ng bawat wafer ay nagsisimula sa pinakakumplikadong M0 transistor layer na may mga pitch na kasing liit ng 30nm (para sa Intel 4 node) gamit ang pinaka-sopistikadong mga tool sa pagmamanupaktura tulad ng EUV scanner. Pagkatapos, ang mga chipmaker ay bubuo ng hindi gaanong kumplikadong mga layer ng transistor sa ibabaw ng una, unti-unting tumataas ang mga laki dahil kailangan nilang ikonekta ang lahat ng mga layer at paganahin ang lahat ng mga transistor.

Ang aktwal na pisikal na mga wire para sa I/O at kapangyarihan ay mukhang napakalaki kung ihahambing sa mga layer ng transistor, at nagiging mas mahirap at mas magastos na iruta ang mga ito nang maayos sa bawat bagong henerasyon.

Ang pagpoproseso ng wafer na may mga chip na nagtatampok ng PowerVia BS PDN ng Intel ay nagsasangkot ng paggawa ng lahat ng kumplikadong layer ng logic pati na rin ang mga signal wire, pagkatapos ay pag-flip ng wafer at pagbuo ng power delivery network ‘sa itaas’ ng logic. Sa papel, mukhang hindi big deal ang naturang ‘flip’. Gayunpaman, nagdaragdag ito ng ilang mga hakbang sa proseso, kabilang ang pag-alis ng ‘labis’ na silicon mula sa wafer upang itayo ang PDN sa ibabaw ng mga logic transistors, CMP clean, metrology, lithography, at etching, upang pangalanan ang ilan.

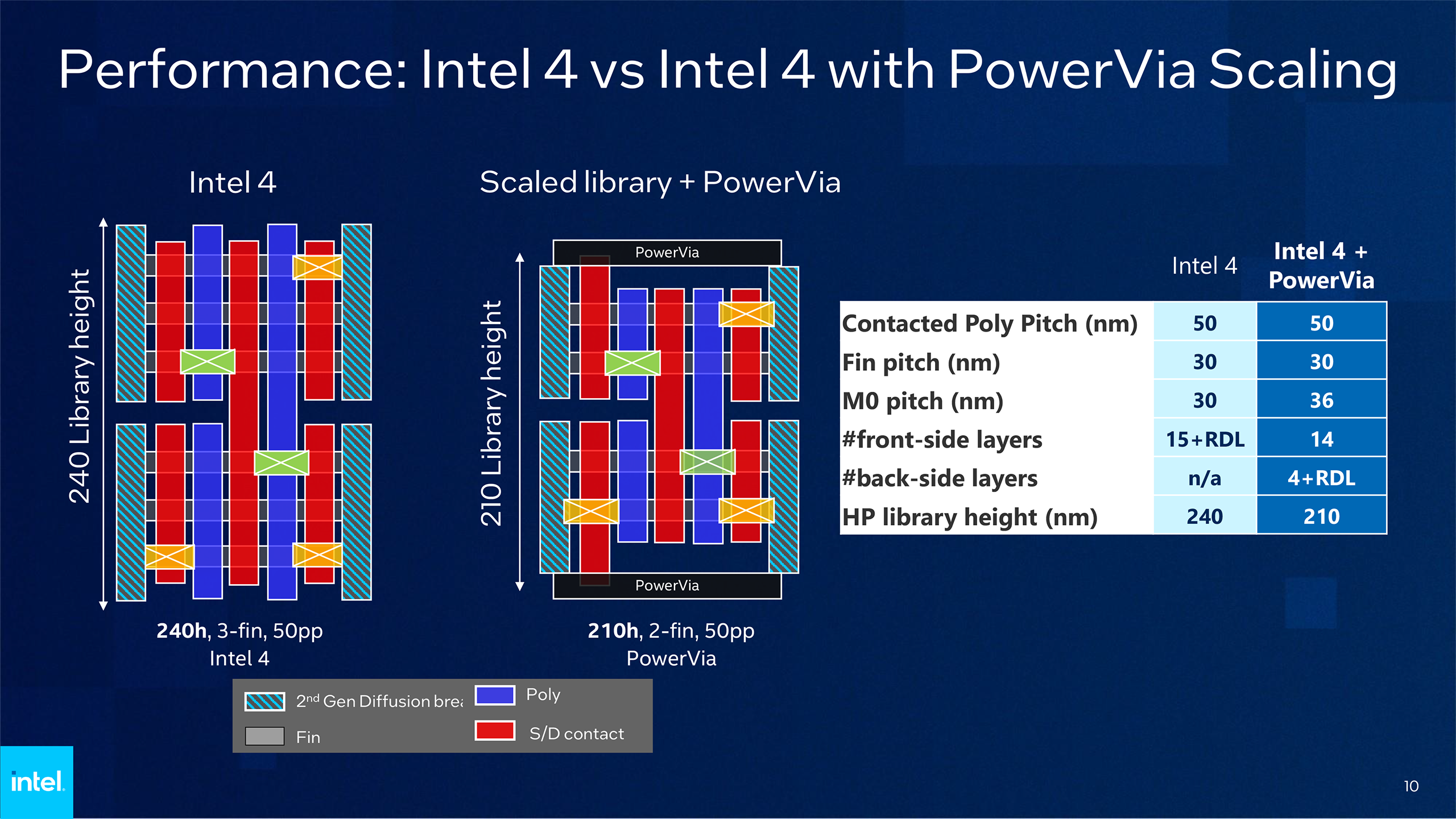

Ang ganitong proseso ng loop ay maaaring hindi nangangailangan ng mga pinaka-advanced na tool sa fab, ngunit nagkakahalaga pa rin ito ng pera. Sa katunayan, ang isang slide ng Intel ay nagpapahiwatig na ang teknolohiya ng proseso ng Intel 4 ay gumagamit ng 15 metallic layer at isang redistribution layer (RDL), samantalang ang Intel 4 + PowerVia ay gumagamit ng 14 na front side layer, apat na back side layer, at isang RDL, na nagpapataas ng kabuuang bilang ng mga layer. hanggang 18 + RDL.

(Kredito ng larawan: Intel)

“Ang mga transistor ay unang binuo, tulad ng dati, kasama ang mga interconnect na layer na idinagdag sa susunod,” sabi ni Ben Sell, vice president ng Technology Development sa Intel. “Ngayon ang nakakatuwang bahagi: i-flip ang wafer at i-polish ang lahat para ilantad ang ilalim na layer kung saan ang mga wire […] para sa kapangyarihan ay konektado. Tinatawag namin itong teknolohiyang silikon, ngunit ang dami ng silikon na natitira sa mga wafer na ito ay talagang napakaliit.”

Mayroong ilang mga kadahilanan upang isaalang-alang sa isang backside PDN. Una, binago nito nang husto ang proseso ng pagmamanupaktura, kaya kinailangan ng Intel na humanap ng paraan upang matiyak ang mataas na ani sa kabila ng mga radikal na pagbabago. Pangalawa, kinailangan ng Intel na tiyakin na ang backside na PDN ay kasing maaasahan ng kasalukuyang PDN nito at gumaganap ayon sa nilalayon. Pangatlo, dahil ang I/O at mga power wire ay matatagpuan na ngayon sa magkabilang panig ng mga transistor, magiging mas mahirap ang paglamig ng mga chips sa hinaharap. Pang-apat, nagiging mas mahirap i-debug ang mga chips dahil kailangan na ngayong alisin ng Intel ang mga backside power interconnects para ma-access ang mga layer ng transistor.

May isa pang kakaiba tungkol sa proseso ng PowerVia ng Intel. Dahil ang Intel ay nag-aalis ng labis na silicon mula sa likod ng wafer, naniniwala itong nawawalan ito ng katigasan, kung kaya’t ito ay nagbubuklod sa isang carrier wafer sa gilid ng signal ng wafer upang hawakan ang konstruksiyon. Ang carrier wafer na iyon ay humihina din sa kalaunan, ngunit ang pagdaragdag nito ay isa ring kumplikado (at malamang na kinakailangan) na hakbang sa proseso.

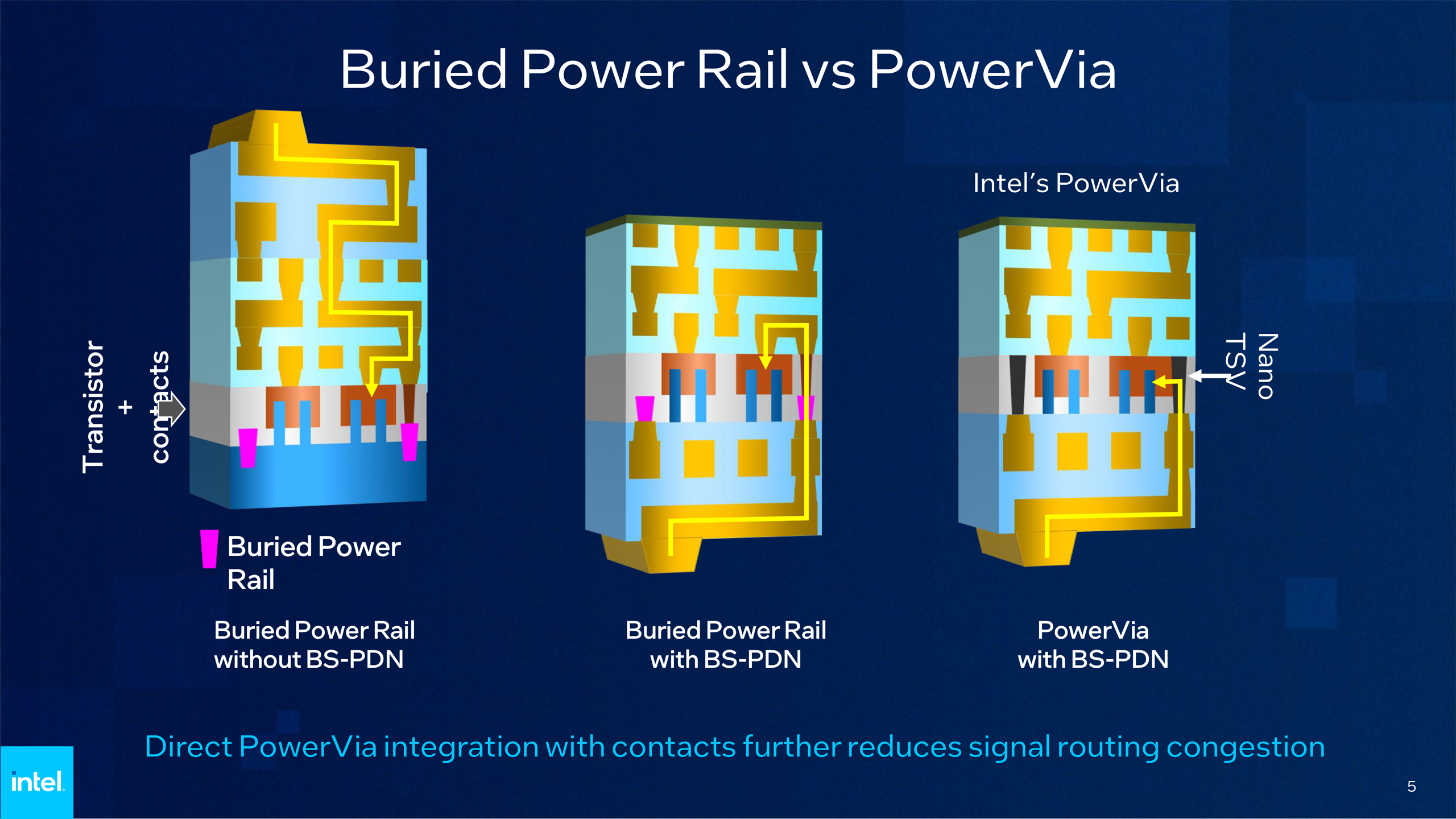

Ang isa pang bagay tungkol sa PowerVia backside PDN ng Intel ay hindi ito gumagamit ng nakabaon na power rails na may BS PDN, ngunit sa halip ay aasa sa nanoscale sa pamamagitan ng silicon vias (TSVs) upang maghatid ng kapangyarihan sa mismong layer ng transistor. Malinaw na ito ang dahilan kung bakit tinawag ng kumpanya ang teknolohiyang PowerVia.

(Kredito ng larawan: Intel)

Pagsubok sa Backside Power Delivery Network

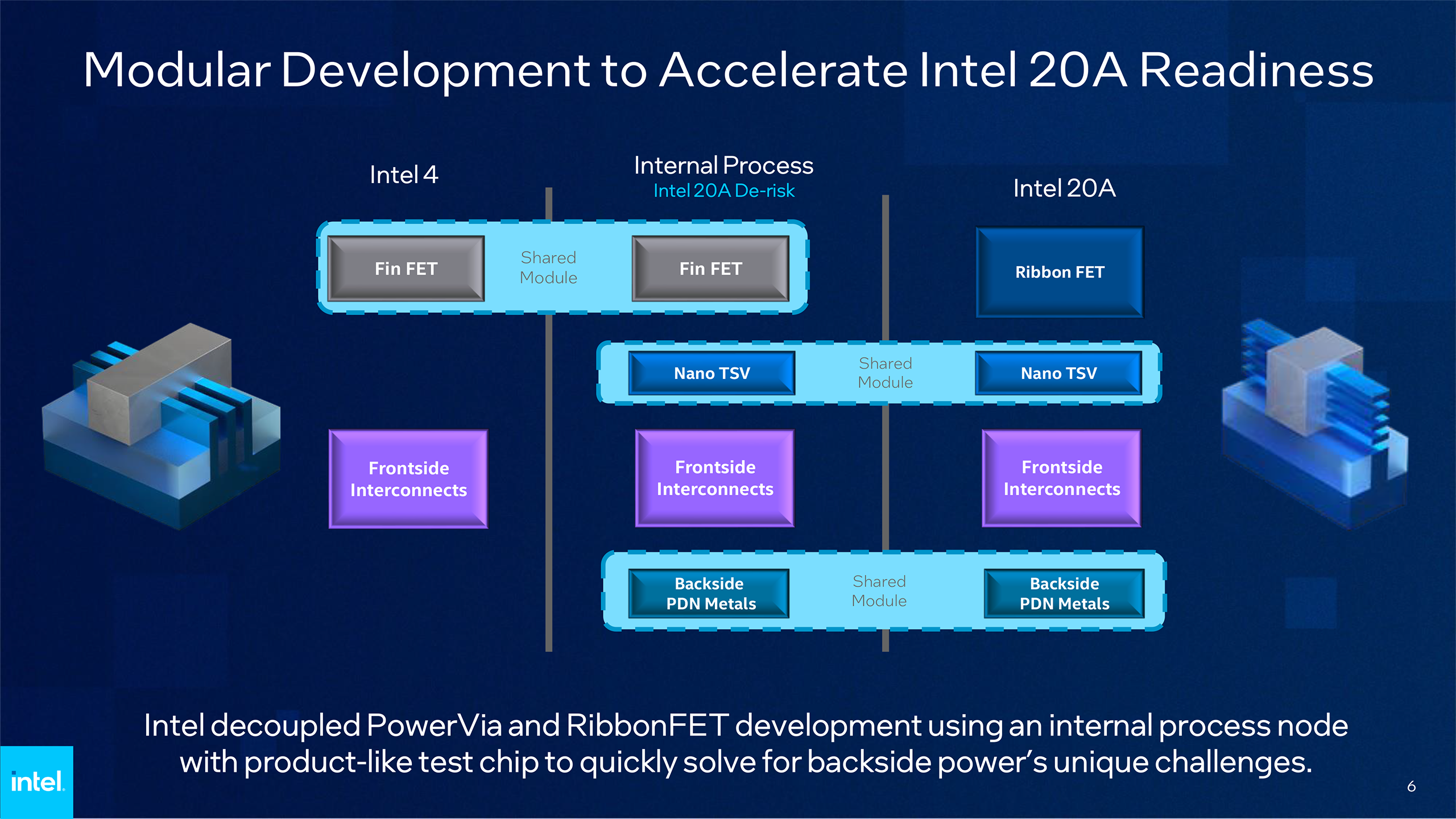

Ngayon na ang Intel ay hindi na ang hindi mapag-aalinlanganang pinuno ng chip market na may pinakamahusay na mga teknolohiya sa proseso, ang kumpanya ay hindi maaaring ipagsapalaran ang isang potensyal na punto ng pagkabigo sa isa sa mga susunod na henerasyong node nito. Kaya, na-decoupled nito ang pagbuo ng RibbonFET GAA transistors at PowerVia BS PDN para gawing mas madali ang proseso ng pagbuo sa pamamagitan ng pagtatrabaho sa RibbonFET na may regular na PDN at pagkatapos ay pag-debug ng PowerVia gamit ang mga napatunayang FinFET.

(Kredito ng larawan: Intel)

Upang subukan ang PowerVia backside power delivery network nito, gumawa ang Intel ng espesyal na proseso ng pagmamanupaktura batay sa Intel 4 node nito na gumagamit ng mga napatunayang FinFET transistors, ngunit may kasama itong backside power rail sa halip na tradisyunal na power rail. Ang prosesong ito ay natural na tinatawag na Intel 4 + PowerVia at ito ay ginagamit para sa isang test chip na may pangalang Blue Sky Creek.

Gumagamit ang Blue Sky Creek test chip ng Intel ng dalawang dies, bawat isa ay nagtatampok ng apat na energy-efficient na core batay sa Crestmont microarchitecture. Ang mga ito ay idinisenyo upang gumana sa 3 GHz sa 1.1 Volts. Ang pansubok na sasakyan ay idinisenyo para sa dalawang layunin lamang: tuklasin ang mga pakinabang ng PowerVia BS PDN at alisin ang panganib sa hinaharap na mga teknolohiyang proseso ng 20A/18A sa pamamagitan ng pagsubok sa lahat ng bagay na nauugnay sa bagong network ng paghahatid ng kuryente, kabilang ang mga ani, pagiging maaasahan ng PDN at ang chip, pagpapalamig, at pag-debug.

Larawan 1 ng 3

(Kredito ng larawan: Intel)

(Kredito ng larawan: Intel)

(Kredito ng larawan: Intel)

Pagdating sa yield, sinabi ng Intel na halos magkapareho ang defect density ng test chip na ipinatupad sa Intel 4 at sa Intel 4 + PowerVia. Natugunan din ng mga layunin ng pagiging maaasahan at mga katangian ng transistor ang mga inaasahan na kinakailangan para sa produksyon. Higit pa rito, ang mga thermal ng pagsubok na sasakyan ay naaayon sa mga inaasahan. Samantala, inamin ng Intel na ang paglamig ay magiging isang hamon sa likurang PDN, kaya nakabuo ito ng mga bagong thermal mitigation scheme upang palamig ang mga next-gen chips.

“Karaniwan mong ginagamit ang silicon side din para sa pagwawaldas ng init,” paliwanag ni Sell. “Kaya, ngayon na-sandwich mo na ang iyong mga transistor at ang tanong ay, ‘Mayroon ba tayong problema sa thermal? Nakakakuha ba tayo ng maraming lokal na pagpainit?’ Sa puntong ito maaari mong hulaan ang sagot: hindi.”

Ang pag-debug ay maaaring isa sa mga pinaka-kumplikadong bahagi, ngunit sa kabutihang-palad ang mga inhinyero ng pagpapatunay ng Intel ay nakahanap ng paraan upang malampasan ang mga paghihirap.

“Nagkaroon ng maraming alalahanin at pag-aatubili at iyon ay marahil ang pinakamahirap na bagay na malaman – kung paano gawin ang pag-debug sa bagong paghahatid ng kuryente sa likod na ito,” sabi ni Sell. “Upang gawing mas mahirap ang mga bagay, sinadyang idinagdag ng test chip design team ang ilang error sa ‘easter egg’ sa chip, lingid sa kaalaman ng validation team. Ang magandang balita? Nakita nila ang mga bug. Nakagawa kami ng napakalaking pag-unlad sa huling dalawang taon sa pagbuo ng mga kakayahan sa pag-debug at pagpapatunay ng mga ito sa Blue Sky Creek.”

Paparating na ang PowerVia BS PDN ng Intel sa 2024

Ang unang available na pampublikong teknolohiya sa proseso ng Intel na gagamitin ang PowerVia backside power delivery network nito ay ang 20A at 18A node nito na magiging handa sa produksyon sa 2H 2023 at 1H 2024, ayon sa pagkakabanggit. Ang unang client CPU ng Intel na gagawin sa proseso ng 20A fabrication ay ang Arrow Lake, na inaasahang ilulunsad malapit sa kalagitnaan ng 2024 o mas maaga.

Ang 18A at 20A na teknolohiya sa pagmamanupaktura ng Intel ay binuo para sa sariling mga produkto ng kumpanya at para sa mga customer ng Intel Foundry Services, kaya nangangako ang PowerVia na maging isang benepisyo para sa Intel at sa mga kliyenteng IFS nito. Magiging tangible benefit man o hindi ang PowerVia BS PDN ay isang bagay lamang ang magsasabi, ngunit kapansin-pansin na ang Intel ang unang kumpanya na handang gumawa ng mga chips na may backside power delivery, dahil ang TSMC ay inaasahang mag-aalok lamang ng katulad na teknolohiya sa huling bahagi ng 2026 hanggang unang bahagi ng 2027.