Lumitaw ang Mga Detalye ng AMD Instinct MI300, Mga Debut sa 2 Exaflop El Capitan Supercomputer

(Kredito ng larawan: Marco Chiappetta)

Ang AMD’s Instinct MI300 ay humuhubog upang maging isang hindi kapani-paniwalang chip na may mga CPU at GPU core at isang mabigat na slab ng high-speed memory na pinagsama sa parehong processor, ngunit ang mga detalye ay nanatiling bahagyang. Ngayon ay nakalap na kami ng ilang bagong detalye mula sa isang International Super Computing (ISC) 2023 presentation na nagbabalangkas sa paparating na two-exaflop El Capitan supercomputer na papaganahin ng Instinct MI300. Natagpuan din namin ang iba pang mga detalye sa isang pangunahing tono mula sa CTO Mark Papermaster ng AMD sa ITF World 2023, isang kumperensya na pinangunahan ng higanteng pananaliksik na imec (mababasa mo ang aming panayam sa Papermaster dito).

Ang El Capitan supercomputer ay nakahanda na maging pinakamabilis sa mundo kapag ito ay nag-on sa huling bahagi ng 2023, na kinuha ang posisyon sa pamumuno mula sa AMD-powered Frontier. Ang makapangyarihang Instinct MI300 ng AMD ay magpapagana sa makina, at ang mga bagong detalye ay kinabibilangan ng topology map ng isang MI300 installation, mga larawan ng AMD’s Austin MI300 lab, at isang larawan ng mga bagong blades na gagamitin sa El Capitan supercomputer. Sasaklawin din namin ang ilan sa iba pang mga bagong development sa paligid ng El Capitan deployment.

Larawan 1 ng 5

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: Hinaharap)

(Kredito ng larawan: Hinaharap)

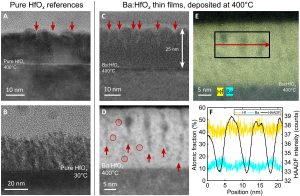

Bilang paalala, ang Instinct MI300 ay isang data center APU na pinagsasama ang kabuuang 13 chiplets, marami sa mga ito ay 3D-stacked, upang lumikha ng isang solong chip package na may dalawampu’t apat na Zen 4 CPU cores na pinagsama sa isang CDNA 3 graphics engine at walo. mga stack ng HBM3 memory na may kabuuang 128GB. Sa pangkalahatan, ang chip ay tumitimbang ng 146 bilyong transistor, na ginagawa itong pinakamalaking chip na ginawa ng AMD sa produksyon. Ang siyam na compute dies, isang halo ng 5nm CPU at GPU, ay 3D-stacked sa ibabaw ng apat na 6nm base dies na mga aktibong interposer na humahawak ng memory at I/O traffic, bukod sa iba pang mga function.

Ang ITF World keynote ng Papermaster ay nakatutok sa layunin ng AMD na “30×25” na pataasin ang power efficiency ng 30x sa 2025, at kung paanong ang pag-compute ay ginagabayan ng power efficiency habang bumabagal ang Batas ni Moore. Ang susi sa inisyatiba na iyon ay ang Instinct MI300, at karamihan sa mga nakuha nito ay nagmumula sa pinasimple na topology ng system na nakikita mo sa itaas.

Gaya ng makikita mo sa unang slide, ang isang node na pinapagana ng Instinct MI250 ay may hiwalay na mga CPU at GPU, na may isang EPYC CPU sa gitna upang i-coordinate ang mga workload.

Sa kaibahan, ang Instinct MI300 ay naglalaman ng built-in na 24-core fourth-gen EPYC Genoa processor sa loob ng package, kaya nag-aalis ng standalone na CPU mula sa equation. Gayunpaman, nananatili ang parehong pangkalahatang topology, sans ang standalone na CPU, na nagpapagana ng isang ganap na konektadong all-to-all na topology na may apat na elemento. Ang ganitong uri ng koneksyon ay nagbibigay-daan sa lahat ng mga processor na makipag-usap sa isa’t isa nang direkta nang walang isa pang CPU o GPU na nagsisilbing tagapamagitan upang maghatid ng data sa iba pang mga elemento, kaya binabawasan ang latency at pagkakaiba-iba. Iyon ay isang potensyal na punto ng sakit sa MI250 topology. Ang MI300 topology map ay nagpapahiwatig din na ang bawat chip ay may tatlong koneksyon, tulad ng nakita natin sa MI250. Ang mga slide ng Papermaster ay tumutukoy din sa mga aktibong interposer na bumubuo sa base na namatay bilang ‘fourth-gen infinity fabric base die.”

Tulad ng makikita mo sa natitira sa mga slide na ito, inilagay ng MI300 ang AMD sa isang malinaw na landas sa paglampas sa mga layunin ng kahusayan nito sa 30X25 habang nalalampasan din ang trend ng kapangyarihan sa industriya. Naghagis din kami ng ilang larawan ng Instinct MI300 na silicon na nakita namin mismo, ngunit sa ibaba ay makikita namin kung paano ang hitsura ng MI300 sa loob ng isang aktwal na talim na ilalagay sa El Capitan.

AMD Instinct MI300 sa El Capitan

Larawan 1 ng 5

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

Sa ISC 2023, si Bronis R. de Supinski, ang CTO para sa Lawrence Livermore National Laboratory (LLNL), ay nagsalita tungkol sa pagsasama ng mga Instinct MI300 APU sa El Capitan supercomputer. Gagamitin ng National Nuclear Security Administration (NNSA) ang El Capitan upang higit pang gamitin ng militar ang nuclear tech.

Tulad ng makikita mo sa unang larawan sa album sa itaas, nagpakita si Supinski ng isang blade para sa sistema ng El Capitan. Ang blade na ito, na ginawa ng system vendor HPE, ay nagtatampok ng apat na liquid-cooled na Instinct MI300 card sa isang slim 1U chassis. Nagpakita rin si Supinksi ng larawan ng Austin lab ng AMD, kung saan mayroon silang MI300 na silicon, kaya ipinapakita na ang mga chip ay totoo at nasa ilalim na ng pagsubok — isang mahalagang punto na dapat gawin kung isasaalang-alang ang ilan sa mga kamakailang maling hakbang sa mga sistemang pinapagana ng Intel.

Madalas na tinutukoy ni Supinksi ang MI300 bilang “MI300A,” ngunit hindi kami sigurado kung iyon ay isang custom na modelo para sa El Capitan o isang mas pormal na numero ng produkto.

Sinabi ni Supinski na ang chip ay may kasamang Infinity Cache ngunit hindi tinukoy ang magagamit na kapasidad. Binanggit din ni Supinski ang kahalagahan ng iisang memory tier nang maraming beses, na binanggit kung paano pinapasimple ng pinag-isang memory space ang programming, dahil binabawasan nito ang mga kumplikado ng paggalaw ng data sa pagitan ng iba’t ibang uri ng compute at iba’t ibang pool ng memorya.

Sinabi ni Supinski na ang MI300 ay maaaring tumakbo sa iba’t ibang mga mode, ngunit ang pangunahing mode ay binubuo ng iisang memory domain at NUMA domain, kaya nagbibigay ng pare-parehong access memory para sa lahat ng CPU at GPU core. Ang pangunahing takeaway ay ang cache-coherent na memorya ay binabawasan ang paggalaw ng data sa pagitan ng CPU at GPU, na kadalasang kumukonsumo ng mas maraming power kaysa sa mismong pag-compute, kaya binabawasan ang latency at pagpapabuti ng performance at power efficiency. Sinabi rin ni Supinksi na medyo madaling mag-port ng code mula sa Sierra supercomputer patungo sa El Capitan.

Ang natitira sa mga slide ni Supinski ay may kasamang impormasyon na isiniwalat na ng AMD, kabilang ang mga projection ng pagganap na 8X ang pagganap ng AI at 5X ang pagganap-per-watt ng MI250X.

Larawan 1 ng 7

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

Binubuo ng HPE ang El Capitan system batay sa Shasta architecture nito at Slingshot-11 networking interconnect. Ito ang parehong platform na nagpapagana sa iba pang exascale supercomputer ng DOE, Frontier, ang pinakamabilis na supercomputer sa mundo, at ang madalas na naantala na Aurora na pinapagana ng Intel silicon.

Kinailangan ng NNSA na bumuo ng mas maraming imprastraktura upang mapatakbo ang Sierra supercomputer at El Capitan nang sabay-sabay. Kasama sa gawaing iyon ang pagpapalakas ng paghahatid ng kuryente na nakatuon sa pagkalkula mula 45 MW hanggang 85 MW. Ang karagdagang 15 MW ng kapangyarihan ay magagamit para sa sistema ng paglamig, na na-upgrade sa 28,000 tonelada sa pamamagitan ng pagdaragdag ng bagong 18,000-toneladang cooling tower. Iyon ay nagbibigay sa site ng kabuuang 100 MW ng kapangyarihan, ngunit ang El Capitan ay inaasahang kumonsumo ng mas mababa sa 40 MW, kahit na ang aktwal na halaga ay maaaring nasa paligid ng 30 MW – ang mga huling numero ay hindi malalaman hanggang sa pag-deploy.

Ang El Capitan ang magiging unang Advanced Technology System (ATS) na gumagamit ng custom na Tri-lab Operating System Software (TOSS) ng NNSA, isang buong stack ng software na binuo sa RHEL.

El Capitan’s Rabbit Program for Storage

Larawan 1 ng 4

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

(Kredito ng larawan: LLNL sa pamamagitan ng ISC 2023)

Gumagamit ang LLNL ng mas maliliit na sistema ng ‘EAS3’ upang patunayan ang software na idi-deploy sa El Capitan kapag naging operational na ito sa huling bahagi ng taong ito. Sinusubukan na ng LLNL ang mga bagong module ng Rabbit na magho-host ng napakaraming SSD para sa malapit na node na lokal na imbakan. Sa itaas, makikita mo ang mga block diagram ng mga node na ito, ngunit tandaan na hindi nila ginagamit ang mga MI300 accelerators — sa halip, mayroon silang mga karaniwang EPYC server processor para sa storage orchestration at data analytics na mga gawain. Ang mabibilis na node na ito ay lumilitaw na nagsisilbing burst buffer na sumisipsip ng napakalaking dami ng papasok na data nang mabilis, na pagkatapos ay isa-shuffle sa mas mabagal na bulk storage system.

Timeline ng AMD Instinct MI300

Sa patuloy na pag-unlad sa isang predictable na ritmo, malinaw na ang El Capitan ay nagpapatuloy sa pagpapatakbo sa huling bahagi ng taong ito. Ang MI300 ay bumubuo ng isang bagong landas para sa mataas na pagganap ng pag-compute na mga handog ng AMD, ngunit sinasabi sa amin ng AMD na ang halo MI300 chips na ito ay magiging mahal at medyo bihira — hindi ito isang mataas na dami ng produkto, kaya hindi sila makakakita ng malawak na deployment tulad ng EPYC Mga CPU ng data center ng Genoa. Gayunpaman, i-filter ng tech ang maraming variant sa iba’t ibang form factor.

Makikipaglaban din ang chip na ito sa Grace Hopper Superchip ng Nvidia, na kumbinasyon ng Hopper GPU at Grace CPU sa parehong board. Ang mga chip na ito ay inaasahang darating sa taong ito. Sinusuportahan ng mga Neoverse-based na Grace CPU ang Arm v9 instruction set, at ang mga system ay may kasamang dalawang chips na pinagsama kasama ng bagong branded na NVLink-C2C interconnect tech ng Nvidia. Sa kabaligtaran, ang diskarte ng AMD ay idinisenyo upang mag-alok ng higit na mahusay na throughput at kahusayan sa enerhiya, dahil ang pagsasama-sama ng mga device na ito sa isang pakete ay karaniwang nagbibigay-daan sa mas mataas na throughput sa pagitan ng mga unit kaysa kapag kumokonekta sa dalawang magkahiwalay na device tulad ng ginagawa ng Grace Hopper.

Ang MI300 ay dapat ding makipagkumpitensya sa Intel’s Falcon Shores, isang chip na unang idinisenyo upang magtampok ng iba’t ibang bilang ng mga compute tile na may mga x86 core, GPU core, at memory sa maraming posibleng configuration. Kamakailan ay naantala ng Intel ang mga ito sa 2025 at muling tinukoy ang mga chips upang itampok ang isang GPU at arkitektura ng AI lamang — hindi na sila magtatampok ng mga core ng CPU. Sa katunayan, naiwan ang Intel na walang direktang kakumpitensya para sa Instinct MI300.

Dahil sa mabilis na paparating na petsa ng power-on para sa El Capitan at reputasyon ng AMD para sa paggawa ng mga supercomputer sa tamang oras, maaari naming asahan ang AMD na magsisimulang magbahagi ng higit pang impormasyon tungkol sa mga Instinct Mi300 APU nito sa lalong madaling panahon. Ang AMD ay magho-host ng Next-Generation Data Center at AI Technology livestream event ng kumpanya sa Hunyo 13, at inaasahan naming matuto pa doon. Tiyaking ihahatid namin sa iyo ang pinakabago mula sa kaganapang iyon pagdating nito.