Inilunsad ng AMD ang Milan-X Gamit ang 3D V-Cache, EPYC 7773X Na May 768MB L3 Cache sa halagang $8,800

(Credit ng larawan: Tom’s Hardware)

Ganap na inihayag ng AMD ang lineup nito ng mga third-gen na EPYC 7003 “Milan-X” na mga processor na may 3D V-Cache ngayon habang inanunsyo nito ang pangkalahatang availability ng mga unang chip sa mundo na ipapadala gamit ang 3D-stacked cache, kaya triple ang halaga ng L3 cache bawat chip. Sinasabi ng AMD na ang mga bagong chip ay nag-aalok ng hanggang 88% na pagpapabuti ng performance sa mga piling teknikal na computing workload, na pinangungunahan ng $8,800 64-core 128-thread EPYC 7773X na may kasamang minsang hindi maiisip na 768MB ng L3 cache. Ibig sabihin, ang isang two-socket server ay maaari na ngayong maglagay ng hanggang 1.5 gigabytes ng L3 cache. Inihayag din ng AMD ang ilang mga bagong detalye tungkol sa teknolohiyang 3D V-Cache nito na paparating din sa mga consumer-oriented na Ryzen 7 5800X3D chips nito sa susunod na buwan.

Naipadala na ng AMD ang mga processor ng Milan-X sa mga hyperscaler, OEM, at SI. Bilang karagdagan, ang Microsoft ay nagbahagi na ng maraming mga benchmark mula sa Milan-X HBv3 VM na magagamit na sa Microsoft Azure, higit sa lahat ay nagpapatunay sa mga paghahabol sa pagganap ng AMD.

Bago ngayon ang pagpepresyo para sa mga chips, at sa ibaba ay makikita natin na ang mga chips ay may upcharge mula sa $910 (11.5%) na pagtaas para sa 64-core EPYC 7773X hanggang sa isang $2,620 (+167%) na upcharge para sa 16-core EPYC 7373X, hindi bababa sa kumpara sa karaniwang pangkalahatang layunin na mga modelo. Gayunpaman, tina-target ng Milan-X ang segment na may mataas na pagganap, kaya mas maihahambing ang frequency-optimized na “F” series na Milan chips. Dito makikita natin na ang Milan-X ay humigit-kumulang 20% na mas mahal kaysa sa mga bahaging iyon.

Ang Intel ay walang anumang direktang maihahambing na mga modelo ng Xeon, ngunit magbabago iyon kapag dumating ang Sapphire Rapids chips na may HBM2E sa huling bahagi ng taong ito. Sinasabi ng Intel na ang mga chip na iyon ay dalawang beses na mas mabilis kaysa sa Milan-X sa ilang mga workload. Natural, kailangan nating makita kung paano ito gumagana sa ating mga lab.

Mga Detalye at Pagpepresyo ng AMD EPYC 7003 Milan-X

Ang EPYC 7003 “Milan-X” ng AMD na Mga Detalye at Proseso ng PagpepresyoPresyo (1KU)Mga Core/ThreadsBase/Boost Clock (GHz)L3 Cache (L3 + 3D V-Cache)TDPcTDP (W)EPYC 7773X$8,80064 / 1282.2 / 3.5768MB280W225-280WEPYC 7763$7,89064 / 1282.45 / 3,5256MB280W225-280WEPYC 7573X$5,950 32 / 642.8 / 3.6768MB280W225-280WEPYC 7F53$3,76132 / 642.8 / 3.7256MB225W225-240WEPYC 7F53 $4,86032 / 642.95 / 4.02W56MB280EPYC 7473X$3,90024 / 482.8 / 3.7768MB240W225-280WEPYC 7443$2,01024 / 482.85 / 4.0128MB200W165-200WEPYC 74F3$2,90024 / 483.2 / 4.02W56MB240EPYC 7373X$4,18516 / 323.05 / 3.8768MB240W225-280WEPYC 7343$1,56516 / 323.2 / 3.9128MB190W165-200WEPYC 73F3$3,52116 / 323.5 / 4.0256MB240W

Pagkatapos ng kinakailangang pag-update ng BIOS, ang mga chip na ito ay bumaba sa mga umiiral nang server na may SP3 socket. Ang teknolohiyang 3D V-Cache ay maaaring maghatid ng mga nakamamanghang pagpapahusay sa pagganap sa ilang mga workload, ngunit ang mga nadagdag na iyon ay hindi nalalapat sa bawat uri ng application. Dahil dito, ang limitadong pagpili ng AMD ng apat na chips, na tinutukoy ng isang ‘X’ suffix, ay kumakatawan sa isang seleksyon ng maingat na piniling mga bilang ng core upang matugunan ang mga partikular na kinakailangan sa teknikal na workload.

Ang mga workload na higit na nakikinabang mula sa 3D V-Cache ay malamang na sensitibo sa L3 cache capacity, may mataas na L3 cache capacity na miss (masyadong malaki ang data para sa cache), o L3 cache conflict na miss (cached data ay may mababang associativity). Ang mga workload na hindi gaanong makikinabang ay may posibilidad na magkaroon ng mataas na mga rate ng hit sa cache, mataas na L3 cache coherency miss (madalas na ibinabahagi ang data sa pagitan ng mga core), o isang beses lang gumamit ng naka-cache na data (sa halip na paulit-ulit).

Lahat ng apat na modelo ng Milan-X ay nilagyan ng walong aktibong core compute die (CCD) upang maihatid ang buong 768 MB ng L3 cache, kahit na may mas maliliit na SKU. Makatuwiran ito dahil may access ang bawat core sa buong 96MB ng L3 cache, kaya kahit na ang pinakamababang-end na 16-core na modelo ay maaaring ganap na magamit ang cache para sa mga application na hindi umaasa sa mabigat na parallelization.

Inaasahan namin ang ilang pagbabago sa bilis ng orasan dahil sa tumaas na cache at mga hamon sa thermal/power na nauugnay sa ganitong uri ng disenyo, ngunit medyo naka-mute ang epekto kumpara sa mga karaniwang pangkalahatang layunin na modelo ng EPYC. Halimbawa, ang EPYC 77373X ay may 250 MHz mas mababang base clock speed ngunit may kaparehong 3.5 GHz boost kumpara sa 7763. Nakikita namin ang 100 hanggang 200 MHz na pagbaba sa base/boost speed sa ilang iba pang SKU, ngunit ang mga pagtanggi na ito ay hindi binibigkas gaya ng kinatatakutan ng ilan.

Ang mga pagsasaayos sa bilis ng orasan ay mas kapansin-pansin kapag nag-zoom out tayo para ikumpara sa mga bahagi ng F-series na naka-optimize sa dalas, na may hanggang 500 MHz na pagbaba sa base frequency at 400 MHz na pagbawas sa mga boost clock. Gayunpaman, ang mga uri ng pagsasaayos na ito ay nag-iiba ayon sa modelo. Ang layunin ng AMD dito ay upang makapaghatid ng mas mataas na pagganap sa pamamagitan ng mas malalaking L3 cache, kaya na-offset ang mga pagsasaayos ng dalas at nag-aalok ng mas pangkalahatang pagganap para sa mga workload na nakikinabang. Nais din ng AMD na panatilihin ang mga processor sa loob ng parehong sobre ng TDP tulad ng mga umiiral na chips upang matiyak ang pagiging tugma sa mga kasalukuyang sistema ng EPYC.

Larawan 1 ng 15

(Image credit: AMD)Larawan 2 ng 15

(Image credit: AMD)Larawan 3 ng 15

(Image credit: AMD)Larawan 4 ng 15

(Image credit: AMD)Larawan 5 ng 15

(Image credit: AMD)Larawan 6 ng 15

(Image credit: AMD)Larawan 7 ng 15

(Image credit: AMD)Larawan 8 ng 15

(Image credit: AMD)Larawan 9 ng 15

(Image credit: AMD)Larawan 10 ng 15

(Image credit: AMD)Larawan 11 ng 15

(Image credit: AMD)Larawan 12 ng 15

(Image credit: AMD)Larawan 13 ng 15

(Image credit: AMD)Larawan 14 ng 15

(Image credit: AMD)Larawan 15 ng 15

(Kredito ng larawan: AMD)

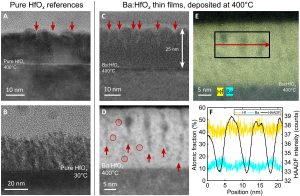

Nagbahagi rin ang AMD ng higit pang mga detalye sa paligid ng 3D V-Cache tech nito. Bilang isang mabilis na pag-refresh, ang 3D V-Cache ay gumagamit ng isang bagong diskarte na gumagamit ng hybrid bonding upang pagsamahin ang isang karagdagang 64MB ng 7nm SRAM cache nang patayo sa ibabaw ng Ryzen compute chiplet, kaya nata-triple ang halaga ng L3 cache bawat die. Mababasa mo ang mga detalye ng malalim na pagsisid dito at dito.

Ilang salik ang nakaimpluwensya sa pagganyak ng AMD na gumamit ng 3D-stacked na SRAM, ngunit ang susi sa mga ito ay ang densidad ng SRAM ay hindi kasing bilis ng densidad ng lohika. Bilang resulta, ang mga cache ay kumonsumo na ngayon ng mas mataas na porsyento ng die area kaysa dati, ngunit hindi naghahatid ng makabuluhang pagtaas ng kapasidad. Higit pa rito, ang pagpapalawak ng cache sa gilid ay magkakaroon ng mas mataas na latency dahil sa haba ng wire at makakain sa magagamit na lugar ng die na magagamit ng AMD para sa mga core. Bilang karagdagan, ang pagdaragdag ng isa pang SRAM chiplet sa isang 2D na layout ay hindi magagawa dahil sa latency at epekto ng bandwidth.

Upang matugunan ang mga isyung iyon, inilalagay ng AMD ang karagdagang SRAM nang direkta sa ibabaw ng gitna ng compute die, na nagpapahintulot sa lower die na maghatid ng kapangyarihan at makipag-usap sa ilalim ng L3 cache chiplet sa pamamagitan ng mga koneksyon sa TSV. Ang mga koneksyon na ito ay patayo na pumupunta sa upper die at fan out, kaya talagang binabawasan ang dami ng data ng distansya na kailangang maglakbay, at sa gayon ang bilang ng mga cycle na kailangan para sa traversal, kumpara sa isang karaniwang planar (2D) na pagpapalawak ng cache. Bilang resulta, ang L3 chiplet ay nagbibigay ng kaparehong 2 TB/s ng peak throughput gaya ng on-die L3 cache, ngunit mayroon lamang itong apat na cycle na latency na parusa.

Ang L3 cache chiplet ay sumasaklaw sa parehong dami ng lugar gaya ng L3 cache sa CCD sa ilalim, ngunit ito ay may dobleng kapasidad. Iyon ay bahagyang dahil ang karagdagang L3 cache slice ay medyo ‘pipi’ — lahat ng control circuitry ay nasa base CCD, na tumutulong na bawasan ang latency na overhead. Gumagamit din ang AMD ng density-optimized na bersyon ng 7nm na dalubhasa para sa SRAM, at mas manipis din ito kaysa sa base die (13 metal layer).

Ang kakulangan ng control circuitry sa L3 chiplet ay nagpapalaki din ng kapasidad at nagbibigay-daan sa AMD na piliing ‘iilawan’ lamang ang mga bahagi ng cache na ina-access, kaya binabawasan (at kahit na inaalis) ang overhead ng kapangyarihan ng pag-triple sa kapasidad ng L3 cache. Bilang karagdagan, dahil binabawasan ng mas malaking cache ang mga biyahe patungo sa pangunahing memorya dahil sa mas mataas na mga rate ng hit ng cache ng L3, ang karagdagang kapasidad ay nagpapagaan ng presyon ng bandwidth sa pangunahing memorya, kaya binabawasan ang latency at sa gayon ay nagpapabuti sa pagganap ng application mula sa maraming mga axes. Ang mas kaunting mga biyahe sa pangunahing memorya ay binabawasan din ang pangkalahatang paggamit ng kuryente.

Ang L3 cache chiplet ay kumokonsumo ng mas kaunting kapangyarihan sa bawat square millimeter kaysa sa mga core ng CPU. Gayunpaman, pinapataas ng vertical stacking ang power density, kaya pinakamahusay na ihiwalay ito sa mga core na bumubuo ng init sa mga gilid ng chiplet. Gayunpaman, mag-iiwan ito ng nakausli na die sa ibabaw ng CCD, kaya gumagamit ang AMD ng isang silicon shim na bumabalot sa tatlong gilid ng L3 chiplet upang lumikha ng pantay na ibabaw para sa heat spreader na nasa ibabaw ng chiplet. Ang Silicon ay isang mahusay na thermal conductor, kaya pinapayagan ng shim ang init na ilipat mula sa mga core hanggang sa heat spreader.

Ang mga nakaraang rendering ng disenyo ay nagpakita ng dalawang natatanging silicon shims at lumalabas na nagpapakita ng L3 cache die na sumasaklaw mula sa isang gilid ng die patungo sa isa pa. Gayunpaman, ang mga materyales ng AMD para sa paglulunsad ng Milan-X ay malinaw na nagpapakita ng isang mahabang shim na sumasaklaw sa compute die at isang manipis na bahagi sa gilid ng die na hindi sakop ng L3 cache chiplet. Kasama sa manipis na kalawakan ng bottom die ang mga function ng I/O na ginagamit ng chiplet para makipag-ugnayan sa I/O die.

Sinasabi ng AMD na walang mga pagbabago sa software ang kinakailangan upang magamit ang tumaas na kapasidad ng cache, kahit na ito ay nakikipagtulungan sa ilang mga kasosyo upang lumikha ng mga sertipikadong software package. Ang mga paketeng iyon ay maaaring makakita ng karagdagang mga pag-optimize ng pagganap, masyadong.

Larawan 1 ng 17

(Image credit: AMD)Larawan 2 ng 17

(Image credit: AMD)Larawan 3 ng 17

(Credit ng larawan: AMD)Larawan 4 ng 17

(Image credit: AMD)Larawan 5 ng 17

(Image credit: AMD)Larawan 6 ng 17

(Image credit: AMD)Larawan 7 ng 17

(Image credit: AMD)Larawan 8 ng 17

(Image credit: AMD)Larawan 9 ng 17

(Image credit: AMD)Larawan 10 ng 17

(Image credit: AMD)Larawan 11 ng 17

(Image credit: AMD)Larawan 12 ng 17

(Image credit: AMD)Larawan 13 ng 17

(Image credit: AMD)Larawan 14 ng 17

(Image credit: AMD)Larawan 15 ng 17

(Image credit: AMD)Larawan 16 ng 17

(Image credit: AMD)Larawan 17 ng 17

(Kredito ng larawan: AMD)

Ang 16- at 24-core na mga modelo ng Milan-X ay partikular na angkop para sa electronic design automation (EDA) software, na malamang na hindi gaanong sinulid. Gayunpaman, ang mamahaling software na ito ay may posibilidad ding maging lisensyado sa per-core na batayan, kaya ang pagkakaroon ng dalawang potensyal na modelo ay nagbibigay-daan sa mga customer na piliin ang kanilang pinakamabuting pagsasaayos. Samantala, ang 24-, 32- at 64-core na mga modelo ay angkop na angkop para sa mas hinihinging sinulid na mga gawain, tulad ng computational fluid dynamics (CFD), finite element analysis (FEA), at structural analysis. Muli, pinapayagan ng hanay ng mga available na core count ang configuration batay sa mga modelo ng paglilisensya.

Nagbigay ang AMD ng sunud-sunod na sarili nitong mga benchmark na galing sa loob, ngunit tulad ng lahat ng data ng pagsubok na ibinigay ng vendor, dapat mong lapitan ito nang may pag-iingat. Isinama namin ang mga tala sa pagsubok sa dulo ng album sa itaas.

Kasama sa mga benchmark ng AMD ang 66% na nakuha para sa 16-core na Milan-X laban sa isang karaniwang modelo ng Milan, ngunit ang mga resulta ay kahanga-hanga laban sa Intel’s Xeon.

Lumiko sa mga high-threaded na workload na may mga flagship chips, sinasabi ng AMD na ang isang dual-socket server na may flagship 64-core 7773X chips nito ay naghahatid ng 44% hanggang 96% na mas maraming performance kaysa sa isang two-socket Intel Xeon 8380 system (40 core chips) sa isang pagpili ng structural analysis, fluid dynamics, at FEA workloads.

Inaasahan mong matatalo ng 128-core EPYC server ang 80-core Intel server, kaya nagbigay din ang AMD ng core-to-core na paghahambing sa parehong mga application na iyon. Dito makikita natin ang 32-core 7573X square off ng AMD kasama ang 32-core Xeon 8382 ng Intel, na tinatalo ito ng 23% hanggang 88% sa parehong mga benchmark na iyon.

Ang AMD ay may kahanga-hangang listahan ng mga kasosyo sa ISV na nagpapatakbo ng gamut ng mga uri ng mga application na pinakamahusay na gumagana sa 3D V-Cache architecture at mayroon ding maraming suporta mula sa mga hardware vendor, tulad ng Supermicro, Dell, Lenovo, HPE, Gigabyte, at QCT, Bukod sa iba pa.

Ang mga processor ng Milan-X ay available sa buong mundo ngayon mula sa mga retailer, at available din ang mga system sa mga OEM. Bukod pa rito, available ang Milan-X sa pamamagitan ng mga HBv3 VM ng Microsoft Azure.

Makukuha ng mga manlalaro ang kanilang mga kamay sa Ryzen 7 5800X3D, ang unang gaming chip na may teknolohiyang 3D V-Cache, sa susunod na buwan.