Inihayag ng Imec ang Sub-1nm Transistor Roadmap, 3D-Stacked CMOS 2.0 Plans

Ibinahagi kamakailan ng Imec, ang pinaka-advanced na semiconductor research firm sa mundo, ang sub-1nm silicon at transistor roadmap nito sa ITF World event nito sa Antwerp, Belgium. Ang roadmap ay nagbibigay sa amin ng ideya ng mga timeline hanggang 2036 para sa susunod na mga pangunahing node ng proseso at mga arkitektura ng transistor na pagsasaliksik at bubuo ng kumpanya sa mga lab nito sa pakikipagtulungan sa mga higante sa industriya, gaya ng TSMC, Intel, Samsung, at ASML, bukod sa marami pang iba. Binalangkas din ng kumpanya ang pagbabago sa tinatawag nitong CMOS 2.0, na magsasangkot ng paghahati-hati sa mga functional unit ng isang chip, tulad ng L1 at L2 cache, sa mga 3D na disenyo na mas advanced kaysa sa mga pamamaraang batay sa chiplet ngayon.

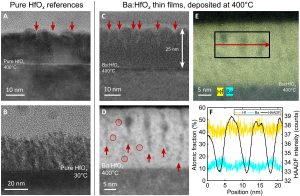

Bilang paalala, ang sampung Angstrom ay katumbas ng 1nm, kaya ang roadmap ng Imec ay sumasaklaw sa mga sub-‘1nm’ na mga node ng proseso. Binabalangkas ng roadmap na ang mga karaniwang FinFET transistor ay tatagal hanggang 3nm ngunit pagkatapos ay lumipat sa bagong disenyo ng Gate All Around (GAA) nanosheet na papasok sa produksyon ng mataas na volume sa 2024. Itinatag ng Imec ang kurso sa mga disenyo ng forksheet sa 2nm at A7 (0.7nm) , ayon sa pagkakabanggit, na sinusundan ng mga pambihirang disenyo tulad ng mga CFET at atomic channel sa A5 at A2.

(Kredito ng larawan: imec)

Ang paglipat sa mas maliliit na node na ito ay nagiging mas mahal sa paglipas ng panahon, at ang karaniwang diskarte ng pagbuo ng mga monolithic chip na may isang solong malaking die ay nagbigay daan sa mga chiplet. Ang mga disenyong nakabatay sa chiplet ay pinaghiwa-hiwalay ang iba’t ibang mga function ng chip sa mga natatanging dies na konektado nang magkasama, kaya pinapayagan ang chip na gumana bilang isang magkakaugnay na yunit – kahit na may mga tradeoff.

Kasama sa pananaw ni Imec sa paradigm ng CMOS 2.0 ang paghiwa-hiwalay ng mga chips sa mas maliliit na piraso, na may mga cache at memory na nahati sa sarili nilang mga unit na may iba’t ibang transistor, pagkatapos ay nakasalansan sa isang 3D na kaayusan sa ibabaw ng iba pang mga function ng chip. Ang pamamaraang ito ay lubos ding sasandal sa mga backside power delivery network (BPDN) na nagruruta ng lahat ng kapangyarihan sa likurang bahagi ng transistor.

Tingnan natin ang imec roadmap at ang bagong pamamaraan ng CMOS 2.0.

Larawan 1 ng 4

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

Tulad ng makikita mo sa album sa itaas, ang industriya ay nahaharap sa tila hindi malulutas na mga hamon habang umuunlad ang mga node, ngunit ang pangangailangan para sa higit na kapangyarihan sa pag-compute, lalo na para sa machine learning at AI, ay tumaas nang husto. Ang kahilingang iyon ay hindi naging madaling matugunan; ang mga gastos ay tumataas habang ang pagkonsumo ng kuryente ay patuloy na tumaas gamit ang mga high-end na chips — ang power scaling ay nananatiling isang hamon dahil ang mga operating voltage ng CMOS ay matigas ang ulo na tumanggi na bumaba sa ibaba 0.7 volts, at ang patuloy na pangangailangan na mag-scale sa mas malalaking chips ay nagpapakita ng kapangyarihan at paglamig na mga hamon na mangangailangan ganap na bagong mga solusyon upang iwasan.

At habang patuloy na dumodoble ang bilang ng transistor sa isang predictable na landas ng Moore’s Law, ang iba pang mga pangunahing isyu ay nagiging mas problemado rin sa bawat bagong henerasyon ng mga chip, tulad ng mga limitasyon ng interconnect bandwidth na lubhang nahuli sa computational na mga kakayahan ng mga modernong CPU at GPU, kaya humahadlang pagganap at nililimitahan ang pagiging epektibo ng mga sobrang transistor na iyon.

Ang imec Transistor at Process Node Roadmap

Larawan 1 ng 6

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

Gayunpaman, ang mas mabilis at mas siksik na mga transistor ang unang priyoridad, at ang unang wave ng mga transistor na iyon ay sasamahan ng Gate All Around (GAA)/Nanosheet na mga device na magde-debut sa 2024 gamit ang 2nm node, na papalitan ang triple-gate FinFETs na nagpapalakas sa nangungunang ngayon. – gilid chips. Ang mga transistor ng GAA ay nagbibigay ng densidad ng transistor at mga pagpapahusay sa pagganap, tulad ng mas mabilis na paglipat ng transistor habang ginagamit ang parehong kasalukuyang drive bilang maramihang mga palikpik. Ang pagtagas ay nababawasan din nang malaki dahil ang mga channel ay napapalibutan ng isang gate, at ang pagsasaayos sa kapal ng channel ay maaaring mag-optimize para sa alinman sa paggamit ng kuryente o pagganap.

Nakita na namin ang ilang mga chipmaker na yumakap sa iba’t ibang variation ng teknolohiyang transistor na ito. Ang pinuno ng industriya na TSMC ay nagpaplano para sa N2 node nito na may GAA na dumating sa 2025, kaya ito ang huling gumamit ng bagong uri ng transistor. Nagtatampok ang quad-sheet RibbonFET ng Intel na may prosesong ‘Intel 20A’ na node ng apat na nakasalansan na nanosheet, bawat isa ay ganap na napapalibutan ng isang gate, at magde-debut sa 2024. Ang Samsung ang unang gumawa ng GAA para sa mga produkto sa pagpapadala, ngunit ang low-volume na SF3E pipe- hindi makakakita ng mass production ang mas malinis na node. Sa halip, ide-debut ng kumpanya ang advanced node nito para sa high volume manufacturing sa 2024.

Bilang paalala, ang sampung Angstrom (A) ay katumbas ng isang 1nm. Ibig sabihin, ang A14 ay 1.4nm, ang A10 ay 1nm, at pupunta tayo sa sub-1nm na panahon sa 2030 timeframe kasama ang A7. Tandaan na ang mga sukatang ito ay kadalasang hindi tumutugma sa aktwal na mga pisikal na dimensyon sa chip, bagaman.

Inaasahan ng Imec na magsisimula ang mga transistor ng forksheet sa 1nm (A10) at tatagal hanggang sa A7 node (0.7nm). Tulad ng makikita mo sa pangalawang slide, ang disenyong ito ay nagsasalansan ng NMOS at PMOS nang hiwalay ngunit hinahati ang mga ito ng isang dielectric na hadlang, na nagbibigay-daan para sa higit na pagganap at/o mas mahusay na density.

Ang mga komplementaryong FET (CFET) transistors ay lalong magpapaliit sa footprint kapag sila ay unang dumating na may 1nm node (A10) noong 2028, na nagbibigay-daan sa mas makapal na naka-pack na standard cell library. Sa kalaunan, makakakita tayo ng mga bersyon ng CFET na may mga atomic na channel, na higit na magpapahusay sa performance at scalability. Ang mga transistor ng CFET, na maaari mong basahin nang higit pa tungkol dito, ay nagsasalansan ng mga aparatong N- at PMOS sa ibabaw ng bawat isa upang paganahin ang mas mataas na density. Dapat markahan ng CFET ang pagtatapos ng pag-scale para sa mga nanosheet device, at ang dulo ng nakikitang roadmap.

Gayunpaman, kakailanganin ang iba pang mahahalagang diskarte para masira ang mga hadlang sa performance, power, at density scaling, na inaakala ng imec ay mangangailangan ng bagong CMOS 2.0 paradigm at system technology co-optimization (SCTO).

STCO at Backside Power Delivery

Larawan 1 ng 11

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

Sa pinakamataas na antas, kinakailangan ng system technology co-optimization (STCO) na muling pag-isipan ang proseso ng disenyo sa pamamagitan ng pagmomodelo ng mga pangangailangan ng system at ang mga target na application at pagkatapos ay gamitin ang kaalamang iyon upang ipaalam ang mga desisyon sa disenyo na napupunta sa paggawa ng chip. Ang pamamaraang ito ng disenyo ay kadalasang nagreresulta sa ‘pagkawatak-watak’ ng mga functional unit na karaniwang makikita bilang bahagi ng isang monolitikong processor, tulad ng power delivery, I/O, at cache, at paghahati-hati sa mga ito sa magkakahiwalay na unit upang ma-optimize ang bawat unit para sa mga kinakailangang katangian ng pagganap sa pamamagitan ng paggamit ng iba’t ibang mga uri ng transistor, at pagkatapos ay nagpapabuti din sa gastos.

Isa sa mga layunin ng ganap na paghiwa-hiwalayin ang karaniwang disenyo ng chip ay ang hatiin ang mga cache/memorya sa kanilang sariling natatanging layer ng isang 3D-stacked na disenyo (higit pa dito sa ibaba), ngunit nangangailangan ito ng pagbawas sa pagiging kumplikado sa tuktok ng chip stack. Ang pagbabago sa mga proseso ng Back End of Line (BEOL), na nakatuon sa pag-wire ng mga transistor nang magkasama at pagpapagana ng parehong komunikasyon (mga signal) at paghahatid ng kuryente, ay susi sa pagsisikap na ito.

Hindi tulad ng mga disenyo ngayon na naghahatid ng kapangyarihan mula sa tuktok ng chip pababa sa mga transistor, ang mga backside power distribution network (BPDN) ay direktang niruruta ang lahat ng kapangyarihan sa likod ng transistor na may mga TSV, kaya naghihiwalay sa paghahatid ng kuryente mula sa mga interconnecting ng paghahatid ng data na nananatili sa kanilang normal na lokasyon sa kabilang panig. Ang paghihiwalay ng power circuitry at ang data-carrying interconnects ay nagpapabuti sa mga katangian ng droop ng boltahe, na nagbibigay-daan para sa mas mabilis na transistor switching habang pinapagana ang mas siksik na pagruruta ng signal sa tuktok ng chip. Ang integridad ng signal ay nakikinabang din dahil ang pinasimple na pagruruta ay nagbibigay-daan sa mas mabilis na mga wire na may pinababang resistensya at kapasidad.

Ang paglipat ng network ng paghahatid ng kuryente sa ilalim ng chip ay nagbibigay-daan sa mas madaling pag-bonding ng wafer-to-wafer sa tuktok ng die, kaya ina-unlock ang potensyal na mag-stack ng logic sa memorya. Iniisip pa nga ng Imec ang posibleng paglipat ng iba pang mga function sa likod ng wafer, tulad ng global interconnect o mga signal ng orasan.

Inihayag na ng Intel ang sarili nitong bersyon ng BPDN technique, na tinatawag na PowerVIA, na magde-debut sa 2024 gamit ang 20A node. Nakatakdang ihayag ng Intel ang higit pang mga detalye tungkol sa teknolohiyang ito sa paparating na kaganapan sa VLSI. Samantala, inanunsyo din ng TSMC na dadalhin nito ang BPDN sa N2P node nito na magiging high-volume production sa 2026, kaya’t ma-lag ito sa Intel nang medyo matagal sa teknolohiyang ito. Sinasabi rin ng Samsung na gamitin ang tech na ito gamit ang 2nm node nito.

CMOS 2.0: Ang Landas sa Tunay na 3D Chips

Larawan 1 ng 16

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

(Kredito ng larawan: imec)

Ang CMOS 2.0 ay ang kulminasyon ng pananaw ng imec para sa hinaharap na mga disenyo ng chip, na sumasaklaw sa ganap na 3D na mga disenyo ng chip. Nakita na namin ang memory stacking gamit ang second-gen 3D V-Cache ng AMD na nag-stack ng L3 memory sa ibabaw ng processor upang palakasin ang kapasidad ng memory, ngunit nakikita ng imec ang buong hierarchy ng cache na nasa sarili nitong mga layer, na may L1, L2, at L3 caches ang pagiging patayo na nakasalansan sa kanilang sariling mga dies sa itaas ng mga transistor na binubuo ng mga processing core.

Ang bawat antas ng cache ay malilikha gamit ang mga transistor na pinakaangkop para sa gawain, ibig sabihin ay mas lumang mga node para sa SRAM, na nagiging mas mahalaga dahil ang SRAM scaling ay nagsimulang bumagal nang husto. Ang pinababang pag-scale ng SRAM ay humantong sa mga cache na kumonsumo ng mas mataas na porsyento ng die, kaya humahantong sa pagtaas ng cost-per-MB at disincentivizing chipmakers mula sa paggamit ng mas malalaking cache. Dahil dito, ang mga pagbawas sa gastos na nauugnay sa paglipat sa hindi gaanong siksik na mga node para sa cache na may 3D stacking ay maaari ding humantong sa mas malalaking cache kaysa sa nakita natin sa nakaraan. Kung ipinatupad nang tama, makakatulong din ang 3D stacking na maibsan ang mga alalahanin sa latency na nauugnay sa mas malalaking cache.

Ang mga diskarteng ito ng CMOS 2.0 ay gagamitin ang 3D stacking technology, tulad ng wafer-to-wafer hybrid bonding, upang bumuo ng direktang die-to-die 3D interconnect, na maaari mong basahin nang higit pa tungkol dito.

Gaya ng makikita mo sa album sa itaas, mayroon ding 3D-SOC roadmap ang Imec na nagbabalangkas sa patuloy na pag-urong para sa mga interconnect na magbubuklod sa mga 3D na disenyo, sa gayon ay nagbibigay-daan sa mas mabilis at mas siksik na mga interconnect sa hinaharap. Ang mga pagsulong na ito ay maisasakatuparan sa pamamagitan ng paggamit ng mga mas bagong uri ng interconnects at mga pamamaraan sa pagproseso sa mga darating na taon.

Tungkol sa imec

Maaaring hindi ka pamilyar sa Interuniversity Microelectronics Center (imec), ngunit kabilang ito sa pinakamahalagang kumpanya sa mundo. Isipin ang imec bilang isang silikon na Switzerland, ng mga uri. Ang Imec ay nagsisilbing isang tahimik na pundasyon ng industriya, na nagdadala ng matitinding karibal tulad ng AMD, Intel, Nvidia, TSMC, at Samsung kasama ng mga chip toolmakers gaya ng ASML at Applied Materials, hindi pa banggitin ang mga kritikal na semiconductor software design companies (EDA) tulad ng Cadence at Synopsys, bukod sa iba pa, sa isang hindi mapagkumpitensyang kapaligiran.

Ang pakikipagtulungang ito ay nagbibigay-daan sa mga kumpanya na magtulungan upang tukuyin ang roadmap ng susunod na henerasyon ng mga tool at software na kanilang gagamitin sa disenyo at paggawa ng mga chips na nagpapagana sa mundo. Ang isang standardized na diskarte ay higit sa lahat sa harap ng malalim na pagtaas ng gastos at pagiging kumplikado ng proseso ng paggawa ng chip. Ang mga nangungunang chipmaker ay gumagamit ng halos parehong kagamitan na nagmula sa ilang kritikal na toolmaker, kaya kailangan ang ilang antas ng standardisasyon, at ang pag-iwas sa mga batas ng pisika ay nangangailangan ng mga pagsisikap sa R&D na maaaring magsimula ng isang dekada nang maaga, kaya ang mga roadmap ng imec ay nagbibigay sa atin ng malawak na tingnan ang paparating na pagsulong sa industriya ng semiconductor.