Ibinahagi ng AMD ang Bagong Second-Gen 3D V-Cache Chiplet na Mga Detalye, hanggang 2.5 TB/s

(Kredito ng larawan: @Locuza_ Twitter)

Ang Ryzen 9 7950X3D ng AMD ay ang pinakamabilis na gaming CPU sa planeta dahil sa desisyon ng AMD na dalhin ang nakakagambalang 3D chip-stacking tech nito sa Zen 4, ngunit nakakagulat, ang kumpanya ay hindi nagbahagi ng anumang mga detalye tungkol sa bago nitong Second-Gen 3D V-Cache sa kanyang Ryzen 7000X3D briefing materials. Una naming nakita ang ilang mga detalye sa isang kamakailang tech conference na isinama namin sa aming pagsusuri, at ngayon ay nasagot na ng AMD ang ilan sa aming mga follow-up na tanong at nagbahagi ng mahahalagang bagong detalye, kasama na ang chiplet ay nananatili sa proseso ng 7nm at mayroon na ngayong peak bandwidth na hanggang 2.5 TB/s, samantalang ang first-gen 3D V-Cache ay umabot sa 2 TB/s (kabilang sa maraming iba pang bagong impormasyon). Mayroon din kaming mga bagong larawan at diagram ng bagong 6nm I/O Die na ginagamit ng AMD para sa mga Ryzen 7000 na processor nito.

Lumipat ang AMD sa second-gen ng 3D V-Cache nito, at walang nakikipagkumpitensyang tech ang Intel. Tinitiyak nito na ang AMD ay mananalo sa parehong pinakamahusay na mga CPU para sa paglalaro at ilang mga application ng data center. Sa pangkalahatan, ang second-gen 3D V-Cache na teknolohiya ng AMD ay isang kahanga-hangang hakbang pasulong sa unang-gen dahil pinapayagan nito ang kumpanya na gamitin ang ngayon-mature at hindi gaanong mahal na 7nm process node para mapalakas ang performance ng cutting-edge na 5nm compute nito mamatay. Ang bagong disenyo ay kumakatawan sa AMD na sinasamantala ang pangunahing bentahe ng mga pamamaraan ng disenyo na nakabatay sa chiplet — gamit ang isang mas luma at hindi gaanong mahal na process node kasabay ng mamahaling bagong teknolohiya ng proseso — sa ikatlong dimensyon. Ngayon para sa mga nitty-gritty na detalye.

Larawan 1 ng 8

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: Tom’s Hardware)

(Kredito ng larawan: Tom’s Hardware)

(Kredito ng larawan: Tom’s Hardware)

(Kredito ng larawan: Tom’s Hardware)

(Kredito ng larawan: Tom’s Hardware)

(Kredito ng larawan: Tom’s Hardware)

Una, isang mabilis na high-level na pag-refresh. Tulad ng makikita mo sa itaas, ang 3D V-Cache tech ng AMD ay nag-stack ng karagdagang L3 SRAM chiplet nang direkta sa gitna ng compute die (CCD) chiplet upang ihiwalay ito sa mga heat-generating core. Ang cache na ito ay nagpapataas ng kapasidad sa 96MB para sa 3D na V-Cache-equipped chiplet, kaya pinapalakas ang pagganap para sa latency-sensitive na mga app, tulad ng paglalaro. Sinaklaw namin ang malalim na mga detalye ng first-gen ng teknolohiyang ito dito.

Nakatanggap kami ng bagong impormasyon sa pagpapatupad ng second-gen na parehong direkta mula sa AMD at mula sa 2023 International Solid-State Circuits Conference (ISSCC), kung saan gumawa ang AMD ng presentasyon sa arkitektura ng Zen 4.

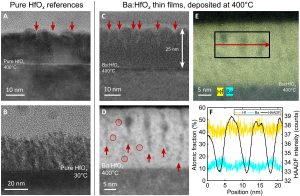

Gumamit ang dating-gen na 3D V-Cache ng AMD ng 7nm L3 SRAM chiplet na nakasalansan sa ibabaw ng 7nm Zen 3 CCD. Ang AMD ay natigil sa proseso ng 7nm para sa bagong L3 SRAM chiplet (tinatawag na ‘L3D’) ngunit ngayon ay inilalagay ito sa ibabaw ng isang mas maliit na 5nm Zen 4 CCD (tingnan ang talahanayan sa ibaba). Lumilikha ito ng hindi pagkakatugma ng laki, gayunpaman, na nangangailangan ng ilang pagbabago.

Mag-swipe para mag-scroll nang pahalangSecond-Gen 3D V-Cache Technology AMD Ryzen 9 7950X3DRow 0 – Cell 0 2nd-Gen 7nm 3D V-Cache DieFirst-Gen 7nm 3D V-Cache Die5nm Zen 4 Core Complex Die (CCD)7nm Zen 3 Core Complex Die (CCD)Size36mm^241mm^266.3 mm^280.7mm^2Transistor Count~4.7 Billion4.7 Billion6.57 Billion4.15 BillionMTr/mm^2 (Transistor Density)~130.6 Million~114.6 Million~99 Million~51.4 Million

Una, ginawa ng AMD na mas maliit ang 7nm SRAM die, kaya sumusukat na ito ngayon ng 36mm2 kumpara sa 41mm2 ng dating gen. Gayunpaman, ang kabuuang bilang ng mga transistor ay nananatiling pareho sa ~4.7 bilyon, kaya ang bagong die ay makabuluhang mas siksik kaysa sa first-gen chiplet.

Tulad ng nakita natin sa first-gen SRAM chiplet, ang 7nm L3 SRAM chiplet ay may hindi kapani-paniwalang transistor density — tinitingnan namin ang halos 3x na density ng first-gen 7nm compute chiplet, at nakakagulat, ang 7nm SRAM chiplet ay mas siksik kaysa sa ang 5nm compute chiplet. Iyon ay dahil, tulad ng dati, ang chiplet ay gumagamit ng isang density-optimized na bersyon ng 7nm na dalubhasa para sa SRAM. Kulang din ito sa karaniwang control circuitry na makikita sa cache — na ang circuitry ay nasa base die, na tumutulong din na mabawasan ang latency sa overhead. Sa kabaligtaran, ang 5nm die ay may kasamang ilang uri ng transistor kasama ang mga path ng data at iba pang mga uri ng mga istruktura na wala sa pinasimpleng L3 SRAM chiplet.

Tulad ng dati, ang sobrang latency mula sa karagdagang L3 SRAM cache ay tumitimbang sa 4 na orasan, ngunit ang bandwidth sa pagitan ng L3 chiplet at ang base die ay tumaas sa 2.5 TB/s, isang 25% na pagpapabuti sa nakaraang 2 TB/s peak.

Ang nakasalansan na L3 SRAM chiplet ay konektado sa base die na may dalawang uri ng through-silicon vias (TSVs — isang vertical electrical connection). Ang mga Power TSV ay nagdadala ng kapangyarihan sa pagitan ng mga chiplet, habang ang mga Signal TSV ay nagdadala ng data sa pagitan ng mga yunit.

Sa unang-gen na disenyo, ang parehong mga uri ng TSV ay naninirahan sa rehiyon ng L3 ng base chiplet. Gayunpaman, ang L3 cache sa base die ay mas maliit na ngayon dahil sa tumaas na density ng 5nm na proseso, at kahit na ang 7nm L3 SRAM chiplet ay mas maliit, ito ngayon ay nag-overlap sa L2 cache (ang naunang gen ay nag-overlap lamang sa L3 sa base. mamatay). Dahil dito, kinailangan ng AMD na baguhin ang mga koneksyon sa TSV sa parehong base die at L3 SRAM chiplet.

Larawan 1 ng 5

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

Kinailangang palawigin ng AMD ang mga power TSV mula sa L3 patungo sa rehiyon ng L2 dahil sa mas maliit na sukat ng 5nm L3 cache sa base die (resulta ng tumaas na density at iba pang mga kadahilanan). Para sa base die, nakamit ng AMD ang 0.68x na epektibong pag-scale ng lugar sa L3 cache, mga path ng data, at control logic kumpara sa lumang 7nm base chiplet, kaya mas kaunting puwang para sa mga TSV sa L3 cache.

Ang mga signal na TSV ay nananatili sa loob ng L3 cache area sa base die, ngunit pinaliit ng AMD ang TSV area sa L3 cache ng 50% sa pamamagitan ng paglalapat ng mga natutunan mula sa first-gen na disenyo kasama ng mga pagpapahusay ng DTCO upang mabawasan ang overhead circuitry sa bagong disenyo ng interface.

Ang 3D chip stacking tech ng AMD ay batay sa teknolohiyang SoIC ng TSMC. Ang SoIC ng TSMC ay bump-less, ibig sabihin, hindi ito gumagamit ng microbumps o solder para ikonekta ang dalawang dies. Marami ka pang mababasa tungkol sa hybrid bonding at proseso ng pagmamanupaktura dito. Sinasabi sa amin ng AMD na ginamit nito ang parehong pangunahing proseso ng pagbubuklod na ipinares sa patuloy na proseso at mga pagpapahusay ng DTCO, ngunit hindi nagbago ang minimum na pitch ng TSV.

Mag-swipe upang mag-scroll nang pahalangRyzen 9 7950X3D Chiplet Boost Frequencies at VoltagesMga Pagsukat ng Hardware ng TomSingle-Threaded PeakMulti-Threaded SustainedVoltage (peak)nT PowerCCD 0 (3D V-Cache)5.25 GHz CD4.85 GHz 3GHz 5.25 GHz CD4.152 GHz dagdag na 3.WC5.8GHz 5.8GHz 3.5GHz 384140W

Ang L3 SRAM chiplet ay nananatili rin sa parehong power domain gaya ng mga CPU core, kaya hindi sila maaaring isaayos nang nakapag-iisa. Nag-aambag ito sa mas mababang frequency sa chiplet na nilagyan ng cache dahil ang boltahe ay hindi maaaring lumampas sa ~1.15V. Maaari mong makita ang aming malalim na pagsubok sa dalawang magkaibang uri ng chiplets dito.

Larawan 1 ng 4

(Kredito ng larawan: Tom’s Hardware)

(Kredito ng larawan: @Locuza_ Twitter)

(Kredito ng larawan: Tom’s Hardware)

(Image credit: Tom’s Hardware) Mag-swipe para mag-scroll nang pahalangRow 0 – Cell 0 6nm I/O Die (IOD) – Ryzen 700012nm I/O Die (IOD) – Ryzen 50006nm I/O Die (IOD) – EPYCSize117.8mm^2125mm^ 2386.88mm^2Transistor Count3.37 Billion2.09 Billion11 billionMTr/mm^2 (Transistor Density)~28.6 Million~16.7 Million~29.8 Million

Kasama rin sa pagtatanghal ng ISSCC ng AMD ang maraming bagong detalye tungkol sa 6nm I/O Dies (IOD) na ginamit sa mga processor ng Ryzen 7000 at EPYC Genoa. Sa album sa itaas, makikita mo ang mga naka-zoom-in na larawan at isang annotated na die shot mula sa chip detective na si @Locuza_. Maaari mo ring palawakin ang tweet sa ibaba upang mabasa ang mahusay na pagsusuri ni Locuza sa Ryzen 7000 IOD.

Inilalagay namin ang mga specs sa talahanayan para sa madaling paghahambing, at tulad ng nakikita mo, ang EPYC Genoa I/O Die ay napakalaki lamang kumpara sa Ryzen 7000 na variant — iyon ay dahil ang AMD ay maaaring mag-wire ng hanggang 12 compute chiplets (CCDs) sa I. /O Mamatay para sa mga EPYC Genoa processor nito.

Sa kabaligtaran, ang mga consumer chip ay limitado sa dalawang chiplet, isang hindi nababagong limitasyon dahil, tulad ng makikita mo sa diagram ni Locuza, ang Ryzen 7000 I/O Die ay mayroon lamang dalawang Global Memory Interconnect 2 (GMI2) na link na nagkokonekta sa mga compute chiplet sa IOD. Iyan ay isang bummer — ang mas mababang core-count na mga modelo ng Genoa na may apat na CCD ay maaaring magkaroon ng dual-GMI3 link (wide mode), isang bagong kakayahan na maaaring mag-alok ng mga pakinabang sa ilang memory throughput-intensive na gawain. Iyon ay magiging kawili-wiling idagdag sa mga chip ng consumer.

Idinagdag din namin ang buong ISSCC 2022 deck sa ibaba para sa iyong pag-aaral — kabilang dito ang ilang iba pang kawili-wiling balita.

Zen 4 Raphael 6 nm client I/O die:- 128b DDR5 PHY + 32b para sa ECC (8b per 32b channel)- 2x GMI3 Port, 3x CCD ay hindi posible. :p- 28x PCIe 5, Zen1/2/3 cIOD ay may 32x PCIe lane. Kaya binawasan ng AMD ang basura para sa merkado ng kliyente. – Talagang isang RDNA2 WGP lang, 128 Shader “Cores” https://t.co/bkqdVvhgrn pic.twitter.com/erYxTw1p8hMarch 4, 2023

Tingnan ang higit pa

Larawan 1 ng 31

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)

(Kredito ng larawan: AMD)